M68HC11K Family Technical Data

HCMOS

Microcontroller Unit

# Freescale Semiconductor, Inc.

# MC68HC11K Family

### **Technical Data**

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

Motorola and

are registered trademarks of Motorola, Inc.

DigitalDNA is a trademark of Motorola, Inc.

© Motorola, Inc., 2001

### **Revision History**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://www.motorola.com/semiconductors

The following revision history table summarizes changes contained in this document. For your convenience, the page number designators have been linked to the appropriate location.

### **Revision History**

| Date          | Revision<br>Level | Description      | Page<br>Number(s) |  |

|---------------|-------------------|------------------|-------------------|--|

| October, 2001 | N/A               | Original release | N/A               |  |

# **Technical Data — M68HC11K Family**

# **List of Sections**

| Section 1. General Description25                 |

|--------------------------------------------------|

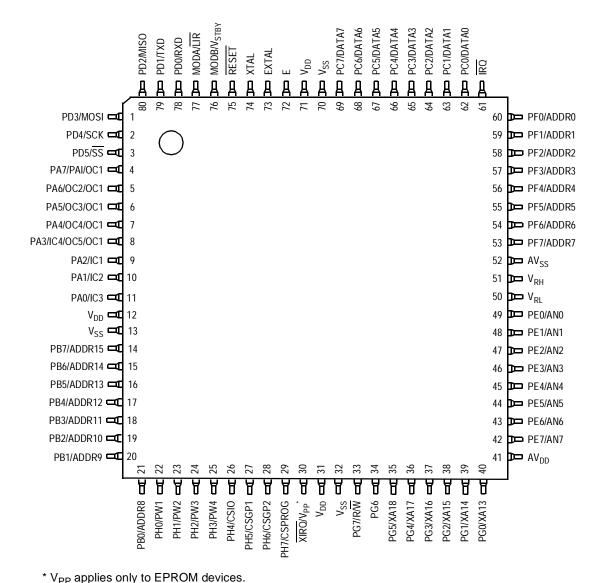

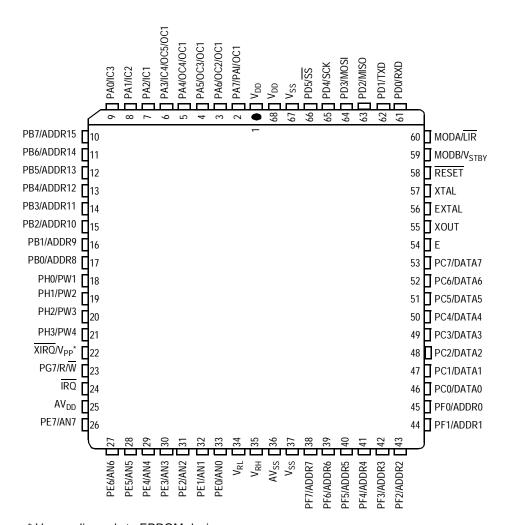

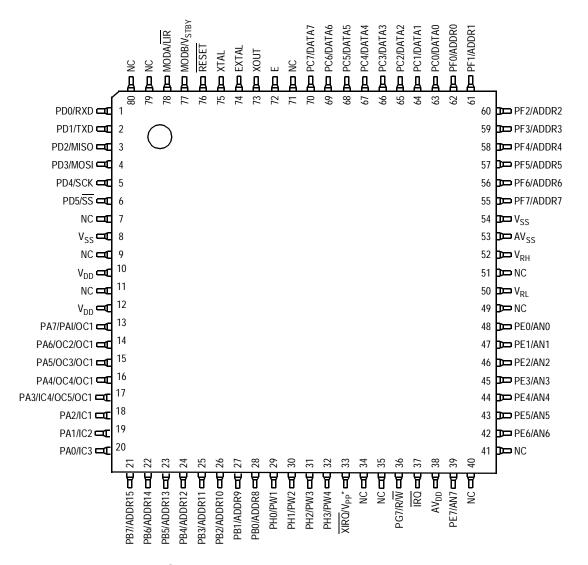

| Section 2. Pin Description31                     |

| Section 3. Central Processor Unit (CPU)45        |

| Section 4. Operating Modes and On-Chip Memory    |

| Section 5. Resets and Interrupts                 |

| Section 6. Parallel Input/Output135              |

| Section 7. Serial Communications Interface (SCI) |

| Section 8. Serial Peripheral Interface (SPI)167  |

| Section 9. Timing System181                      |

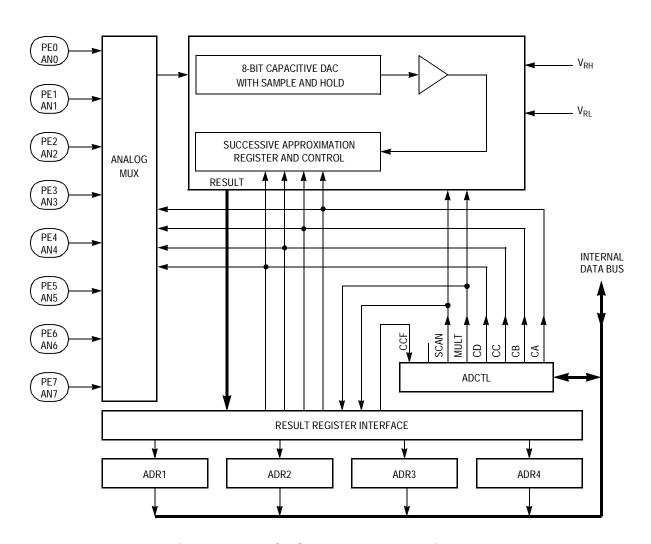

| Section 10. Analog-to-Digital (A/D) Converter    |

| Section 11. Memory Expansion and Chip Selects231 |

| Section 12. Electrical Characteristics           |

| Section 13. Mechanical Data273                   |

| Section 14. Ordering Information281              |

| Section 15. Development Support283               |

| Index285                                         |

| Technical Data                                   |

MOTOROLA

M68HC11K Family

List of Sections

# **Technical Data — M68HC11K Family**

# **Table of Contents**

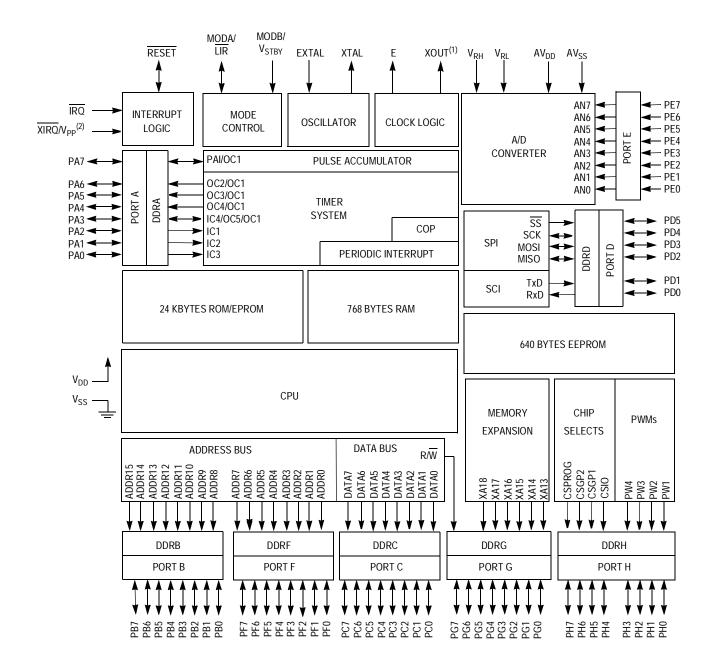

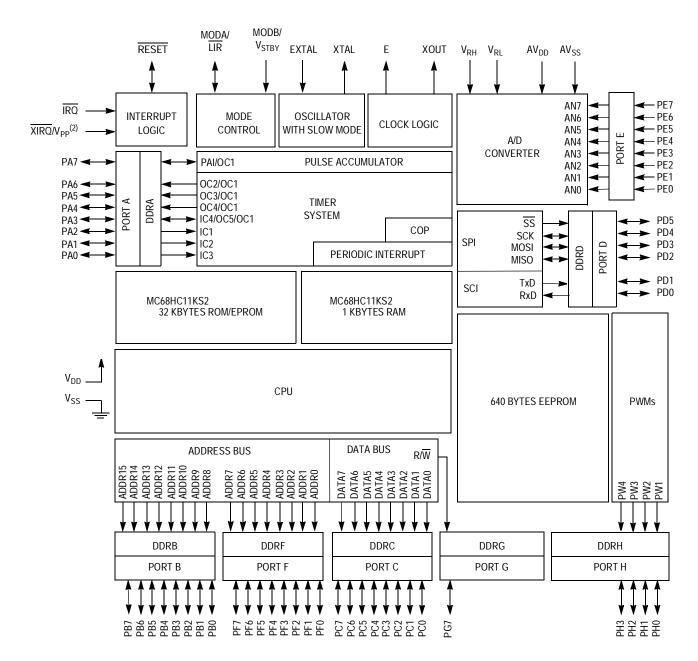

# **Section 1. General Description**

| 1.1  | Contents                                                                                                |

|------|---------------------------------------------------------------------------------------------------------|

| 1.2  | Introduction                                                                                            |

| 1.3  | M68HC11K Family Members                                                                                 |

| 1.4  | Features                                                                                                |

| 1.5  | Structure                                                                                               |

|      | Section 2. Pin Description                                                                              |

| 2.1  | Contents                                                                                                |

| 2.2  | Introduction                                                                                            |

| 2.3  | Power Supply (V <sub>DD</sub> , V <sub>SS</sub> , AV <sub>DD</sub> , and AV <sub>SS</sub> )             |

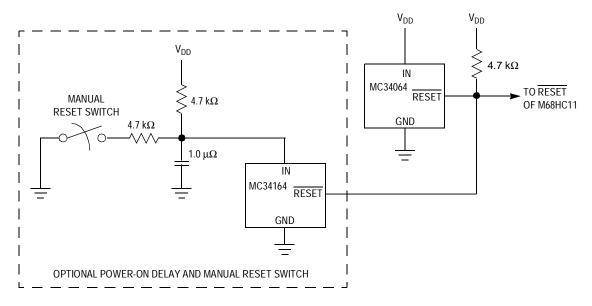

| 2.4  | Reset (RESET)                                                                                           |

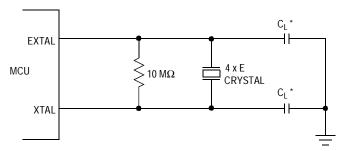

| 2.5  | Crystal Driver and External Clock Input (XTAL and EXTAL) 37                                             |

| 2.6  | XOUT                                                                                                    |

| 2.7  | E-Clock Output (E)                                                                                      |

| 2.8  | Interrupt Request (IRQ) and Non-Maskable Interrupt (XIRQ) .38                                           |

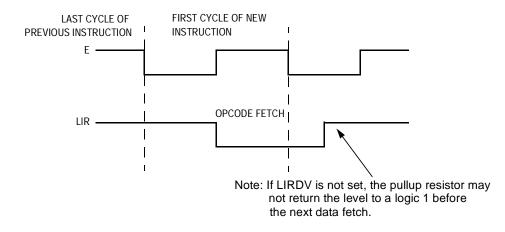

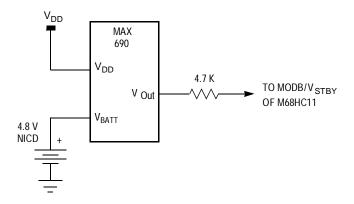

| 2.9  | Mode Selection, Instruction Cycle Reference, and Standby Power (MODA/LIR and MODB/V <sub>STBY</sub> )39 |

| 2.10 | V <sub>RH</sub> and V <sub>RL</sub> 41                                                                  |

| 2.11 | Port Signals                                                                                            |

# **Section 3. Central Processor Unit (CPU)**

| 3.1                                                                                                    | Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.2                                                                                                    | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

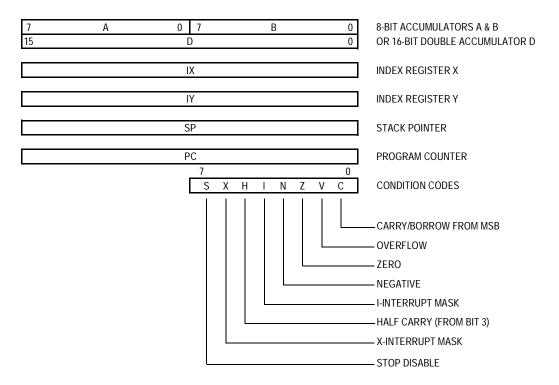

| 3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6<br>3.3.6<br>3.3.6<br>3.3.6<br>3.3.6<br>3.3.6 | CPU Registers       .46         Accumulators A, B, and D (ACCA, ACCB, and ACCD)       .47         Index Register X (IX)       .47         Index Register Y (IY)       .47         Stack Pointer (SP)       .48         Program Counter (PC)       .50         Condition Code Register (CCR)       .50         1 Carry/Borrow (C)       .50         2 Overflow (V)       .50         3 Zero (Z)       .50         4 Negative (N)       .51         5 Interrupt Mask (I)       .51 |

| 3.3.6.0<br>3.3.6.7                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3.3.6.                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3.4                                                                                                    | Data Types                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3.5                                                                                                    | Opcodes and Operands                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.6<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4<br>3.6.5<br>3.6.6                                              | Addressing Modes       .53         Immediate       .54         Direct       .54         Extended       .54         Indexed       .54         Inherent       .55         Relative       .55                                                                                                                                                                                                                                                                                       |

| 3.7                                                                                                    | Instruction Set55                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

### **Section 4. Operating Modes and On-Chip Memory**

| 4.1                                              | Contents                                                                                                               | 63                       |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 4.2                                              | Introduction                                                                                                           | 64                       |

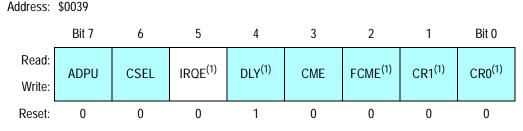

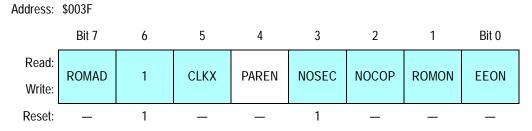

| 4.3                                              | Control Registers                                                                                                      | 64                       |

| 4.4                                              | System Initialization                                                                                                  | .76                      |

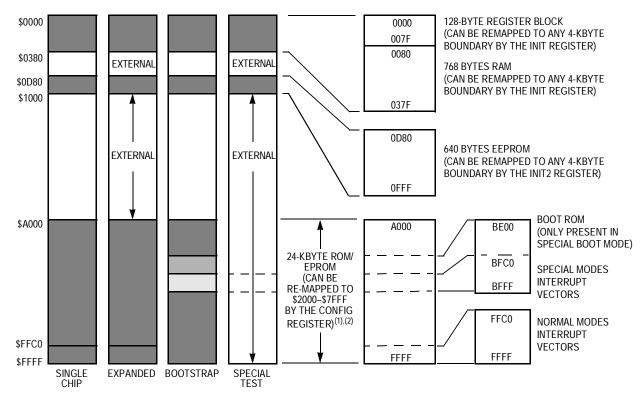

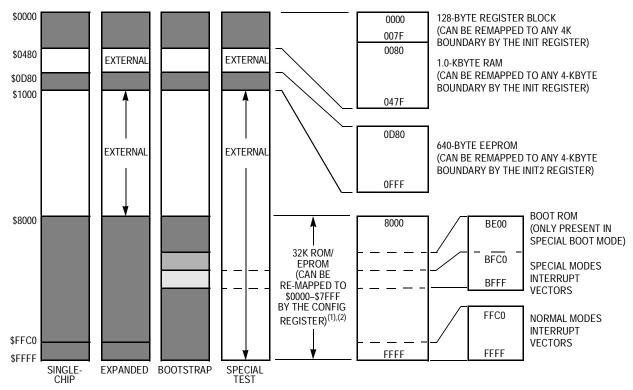

| 4.5<br>4.5.1<br>4.5.2<br>4.5.3<br>4.5.4<br>4.5.5 | Operating Modes Single-Chip Mode Expanded Mode Bootstrap Mode Special Test Mode Mode Selection                         | .77<br>.77<br>.78<br>.79 |

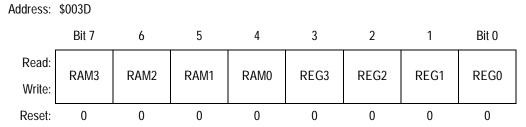

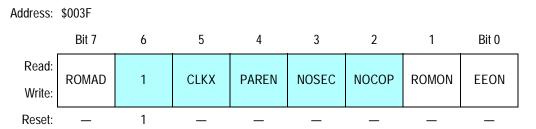

| 4.6<br>4.6.1<br>4.6.2<br>4.6.3<br>4.6.4          | Memory Map.  Control Registers and RAM  ROM or EPROM.  EEPROM  Bootloader ROM.                                         | .84<br>.87<br>.87        |

| 4.7<br>4.7.1<br>4.7.2                            | EPROM/OTPROM (M68HC711K4 and M68HC711KS2) Programming the EPROM with Downloaded Data Programming the EPROM from Memory | 90                       |

| 4.8<br>4.8.1                                     | EEPROM and the CONFIG Register                                                                                         | .93                      |

| 4.8.1.2<br>4.8.1.2                               | 3 - 3 - 3                                                                                                              |                          |

| 4.8.1.3                                          |                                                                                                                        |                          |

| 4.8.2                                            | EEPROM Programming                                                                                                     | .97                      |

| 4.8.2.                                           | 3 3                                                                                                                    |                          |

| 4.8.2.3<br>4.8.2.3                               |                                                                                                                        |                          |

| 4.8.2.4                                          |                                                                                                                        |                          |

| 4.8.3                                            | CONFIG Register Programming                                                                                            |                          |

| 4.8.4                                            |                                                                                                                        | 100                      |

# **Table of Contents**

| 4.9 XOUT Pin Control102                          |

|--------------------------------------------------|

| 4.9.1 System Configuration Register102           |

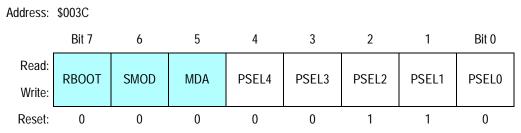

| 4.9.2 System Configuration Options 2 Register    |

|                                                  |

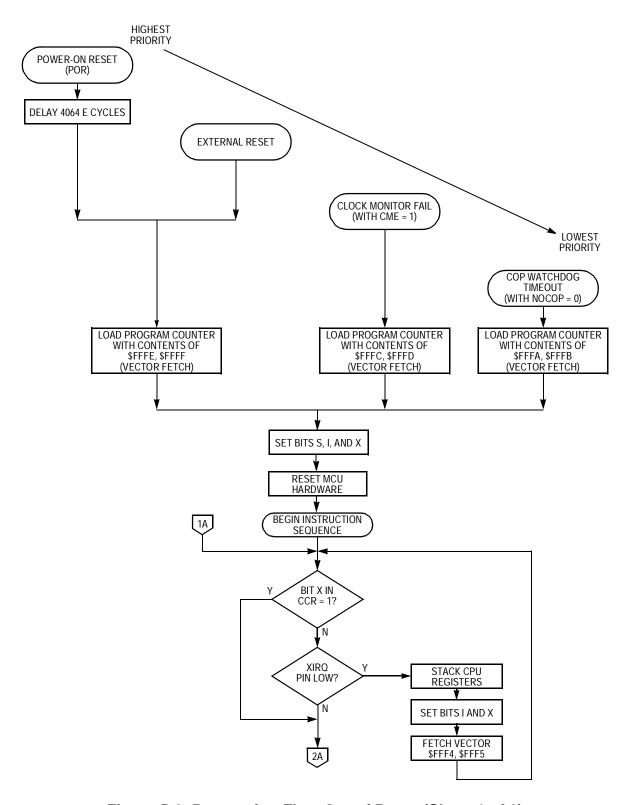

| Section 5. Resets and Interrupts                 |

| 5.1 Contents                                     |

| 5.2 Introduction                                 |

| 5.3 Sources of Resets                            |

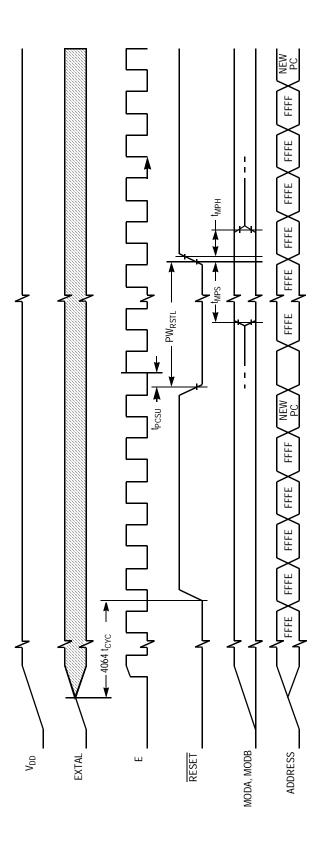

| 5.3.1 Power-On Reset (POR)                       |

| 5.3.2 External Reset (RESET)                     |

| 5.3.3 Computer Operating Properly (COP) System   |

| 5.3.3.1 System Configuration Register            |

| 5.3.3.2 System Configuration Options Register109 |

| 5.3.3.3 Arm/Reset COP Timer Circuitry Register   |

| 5.3.4 Clock Monitor Reset110                     |

| 5.3.4.1 System Configuration Options Register111 |

| 5.3.4.2 System Configuration Options Register 2  |

| 5.4 Effects of Reset                             |

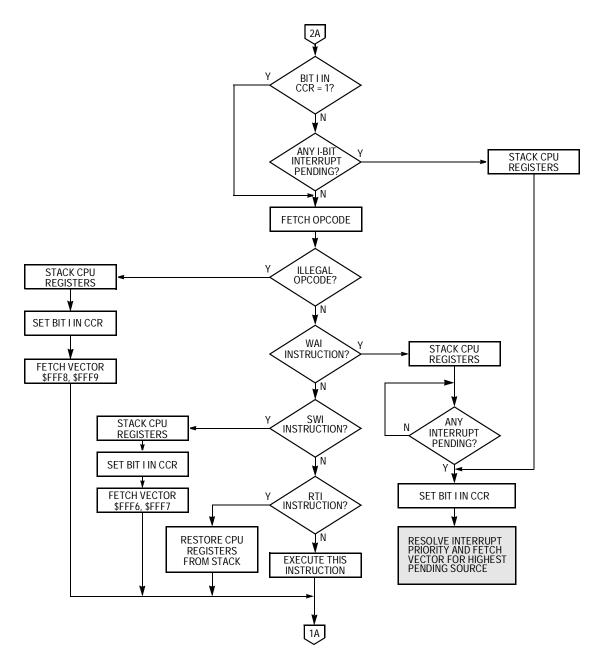

| 5.5 Interrupts117                                |

| 5.5.1 Non-Maskable Interrupts                    |

| 5.5.1.1 Non-Maskable Interrupt Request (XIRQ)120 |

| 5.5.1.2 Illegal Opcode Trap                      |

| 5.5.1.3 Software Interrupt (SWI)                 |

| 5.5.2 Maskable Interrupts                        |

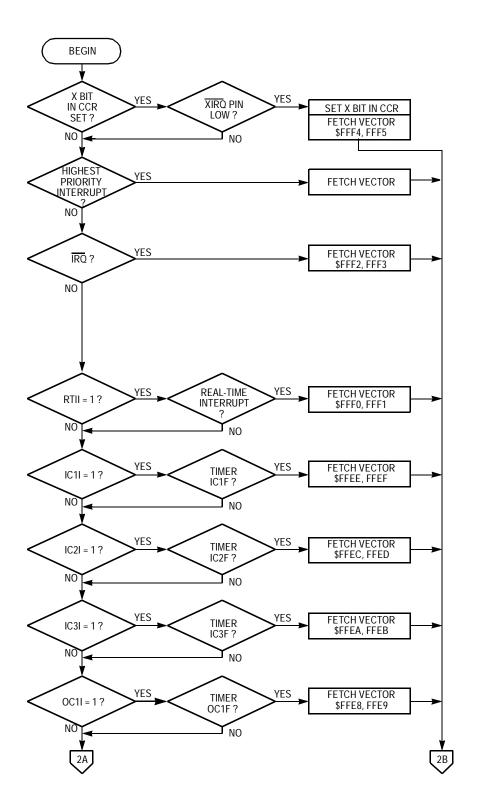

| 5.6 Reset and Interrupt Priority122              |

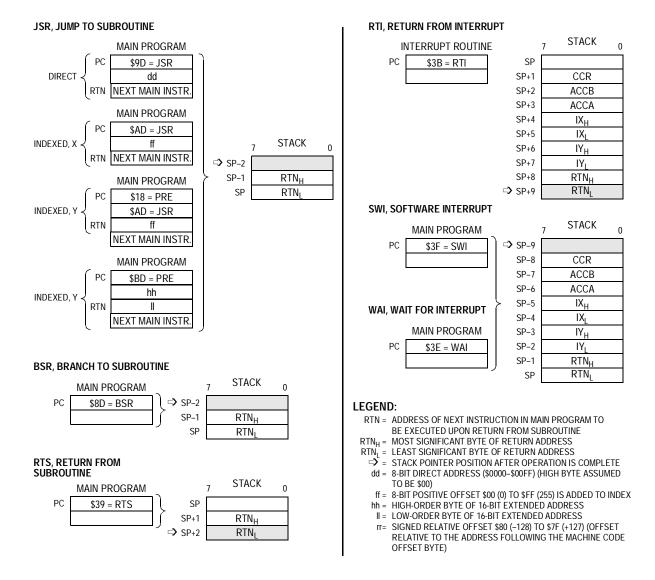

| 5.7 Reset and Interrupt Processing123            |

| 5.8 Low-Power Operation129                       |

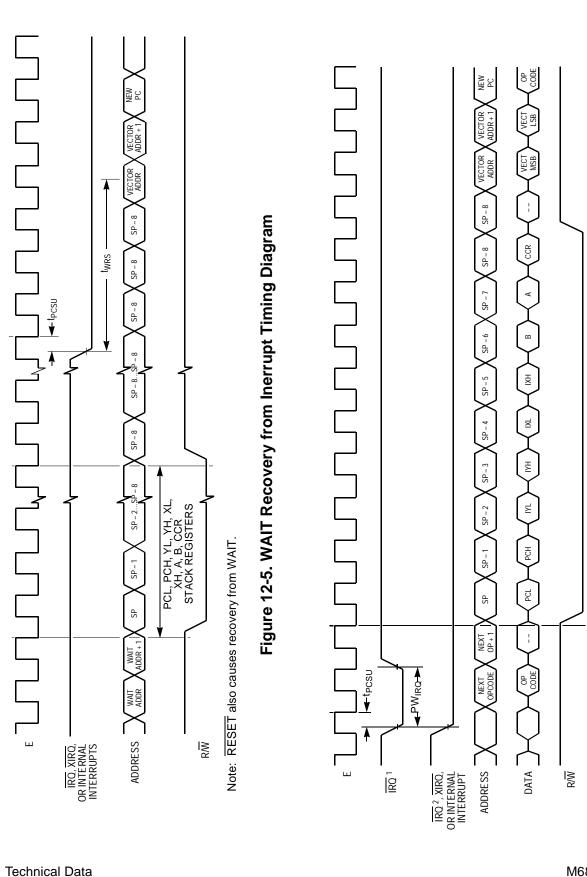

| 5.8.1 Wait Mode                                  |

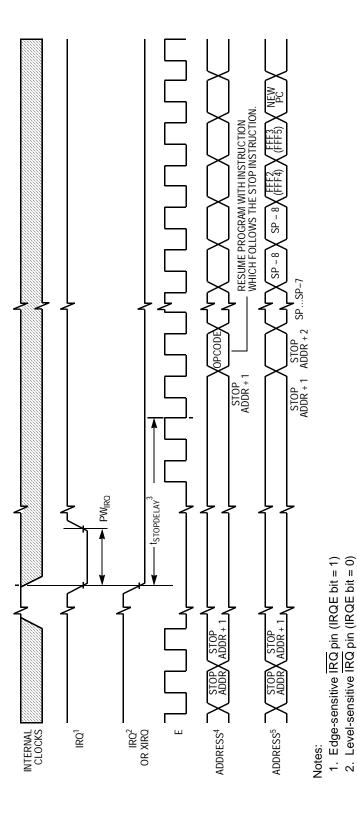

| 5.8.2 Stop Mode                                  |

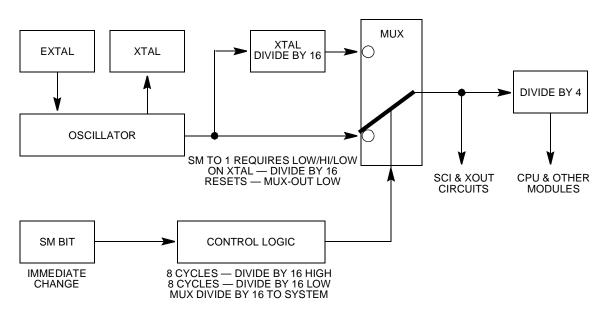

| 5.8.3 Slow Mode                                  |

### Section 6. Parallel Input/Output

|      | ·                                                |

|------|--------------------------------------------------|

| 6.1  | Contents                                         |

| 6.2  | Introduction                                     |

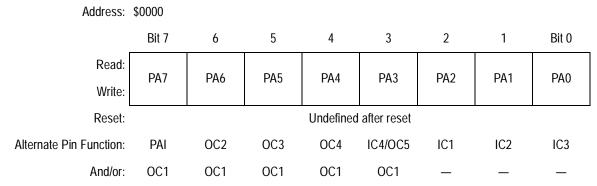

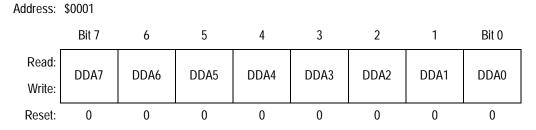

| 6.3  | Port A                                           |

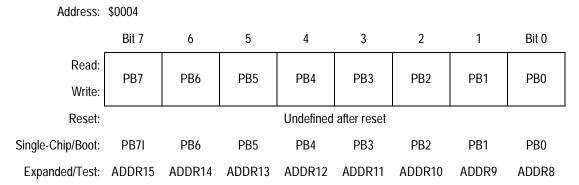

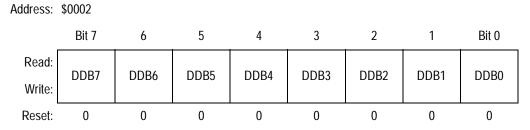

| 6.4  | Port B                                           |

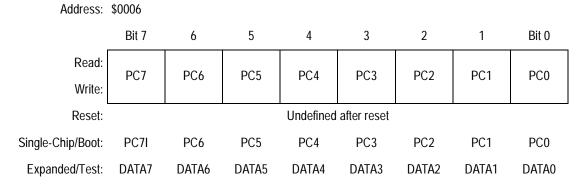

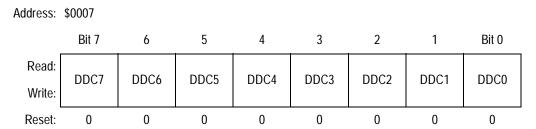

| 6.5  | Port C                                           |

| 6.6  | Port D                                           |

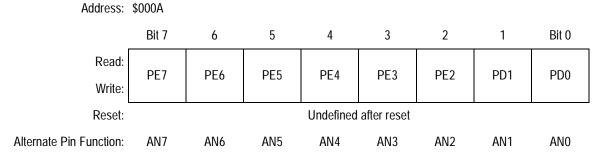

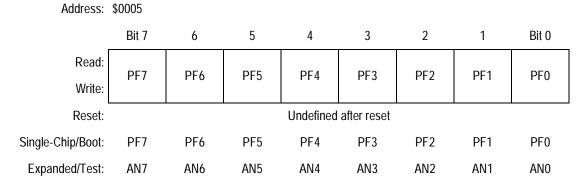

| 6.7  | Port E                                           |

| 6.8  | Port F                                           |

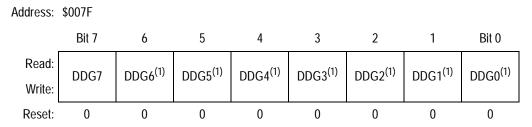

| 6.9  | Port G                                           |

| 6.10 | Port H                                           |

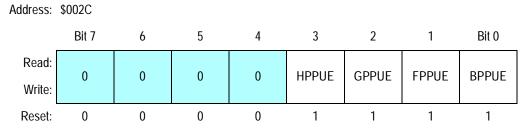

| 6.11 | Internal Pullup Resistors147                     |

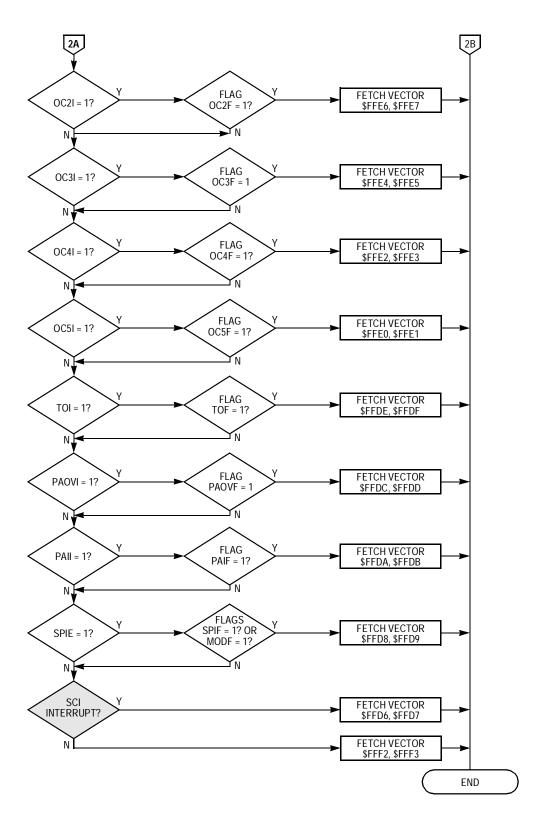

| 5    | Section 7. Serial Communications Interface (SCI) |

| 7.1  | Contents                                         |

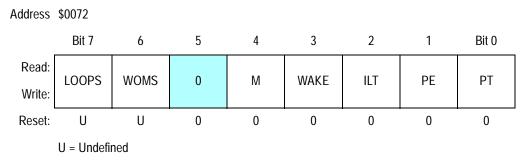

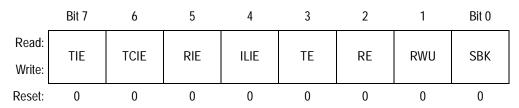

| 7.2  | Introduction                                     |

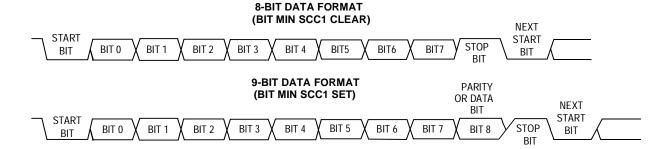

| 7.3  | Data Format                                      |

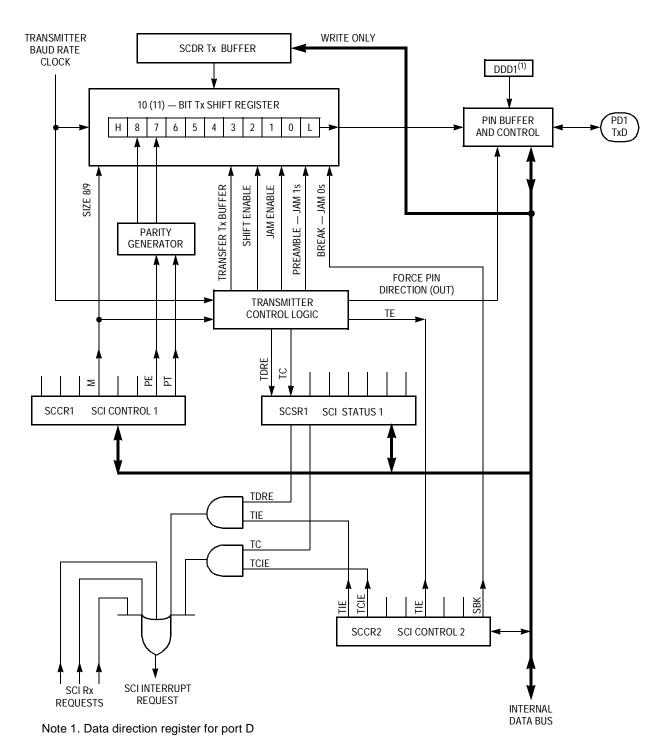

| 7.4  | Transmit Operation                               |

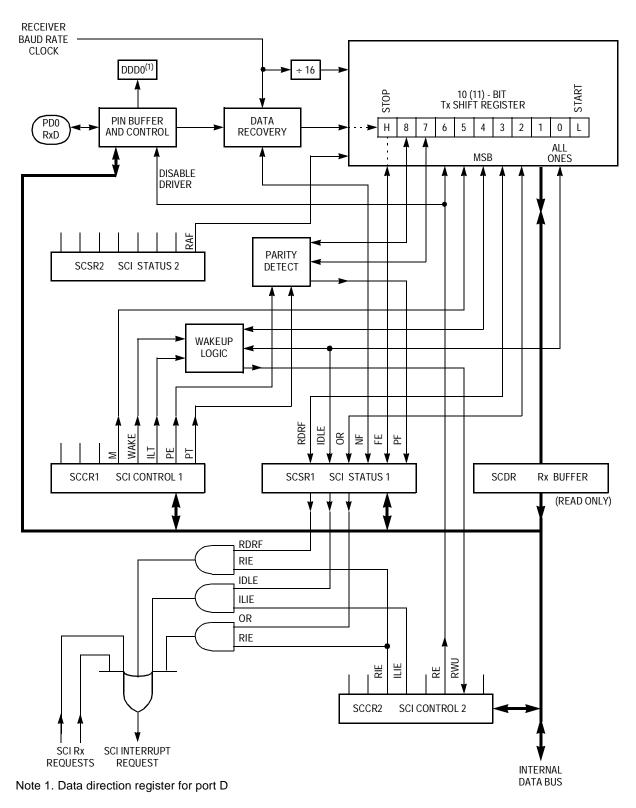

| 7.5  | Receive Operation                                |

| 7.6  | Wakeup Feature                                   |

| 7.7  | Short Mode Idle Line Detection                   |

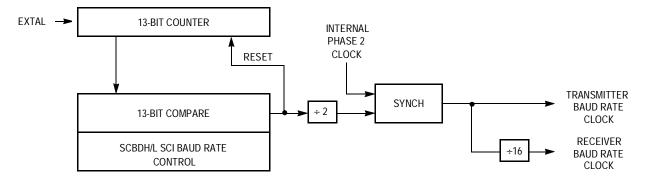

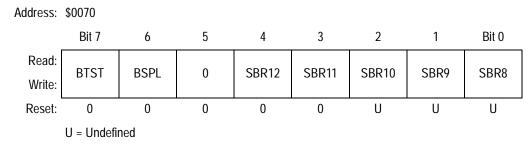

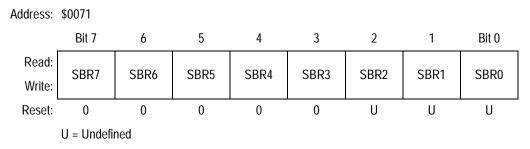

| 7.8  | Baud Rate Selection                              |

|      |                                                  |

12

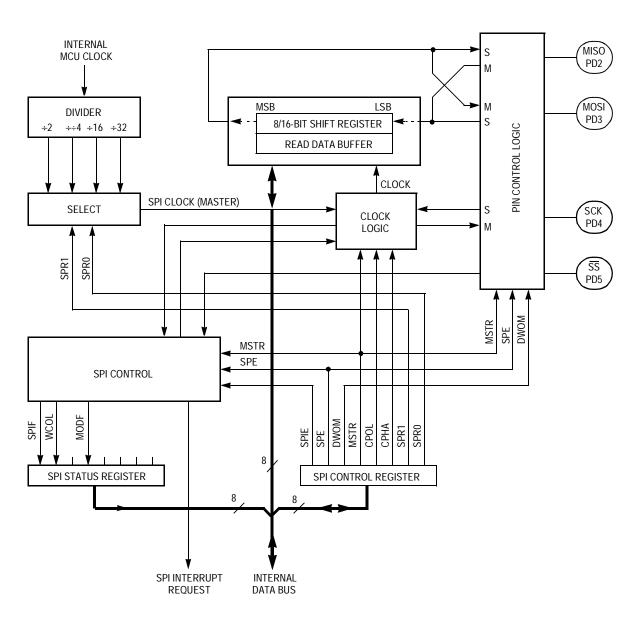

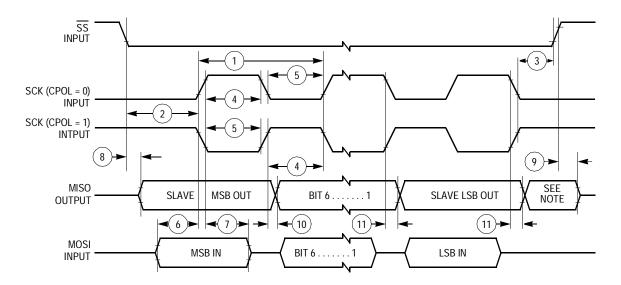

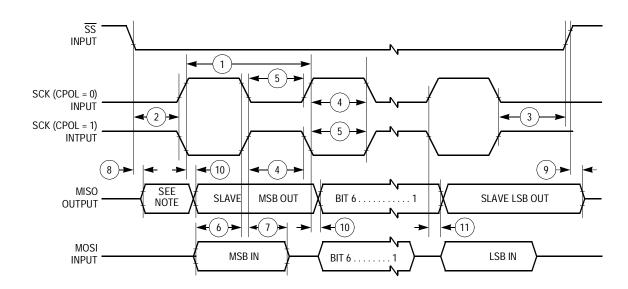

# Section 8. Serial Peripheral Interface (SPI)

| 8.1                                              | Contents                                                                                                                                                                                                                          |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8.2                                              | Introduction                                                                                                                                                                                                                      |

| 8.3                                              | SPI Functional Description                                                                                                                                                                                                        |

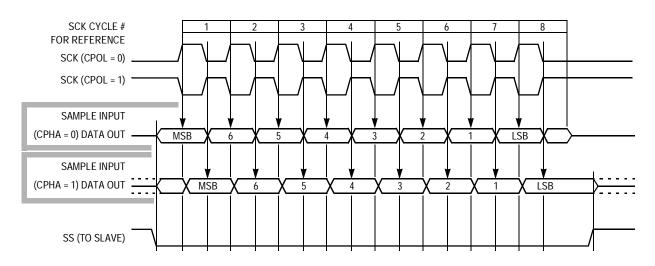

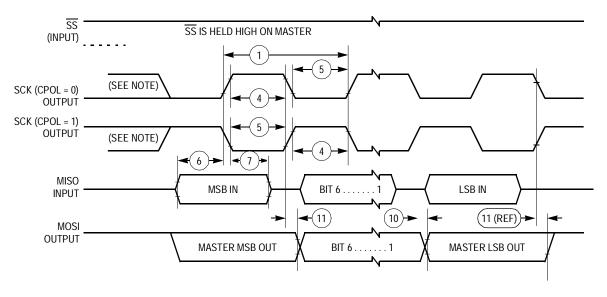

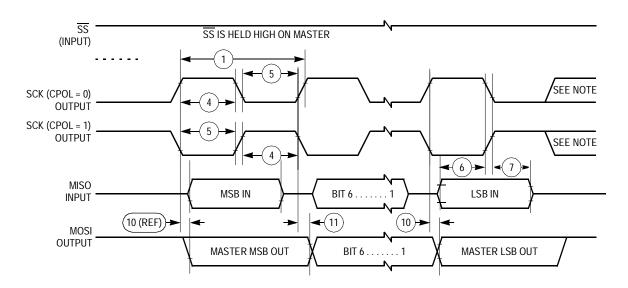

| 8.4<br>8.4.1<br>8.4.2<br>8.4.3<br>8.4.4<br>8.4.5 | SPI Signal Descriptions       170         Master In Slave Out (MISO)       170         Master Out Slave In (MOSI)       170         Serial Clock (SCK)       170         Slave Select (SS)       171         SPI Timing       171 |

| 8.5<br>8.5.1<br>8.5.2                            | SPI System Errors172Mode Fault Error172Write Collision Error173                                                                                                                                                                   |

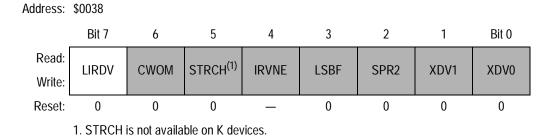

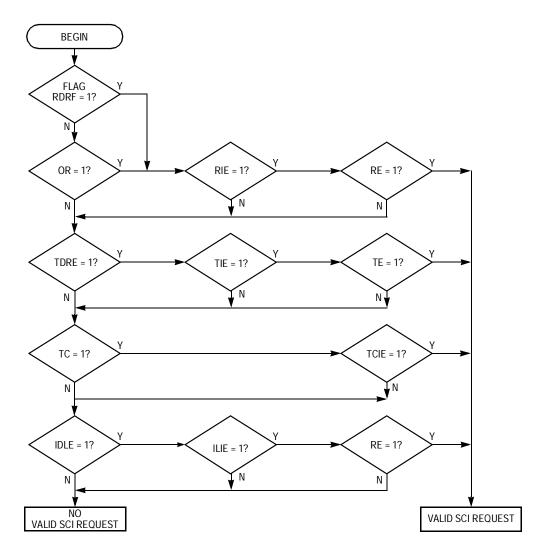

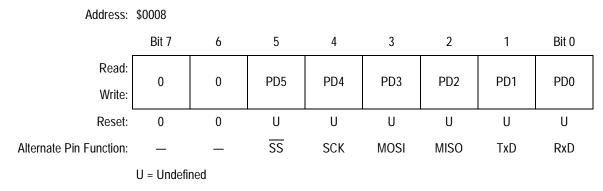

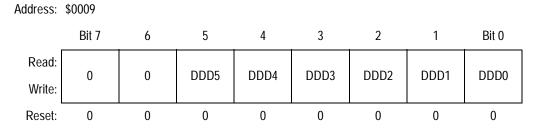

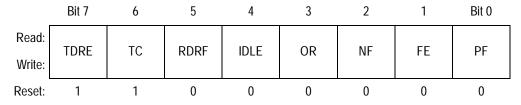

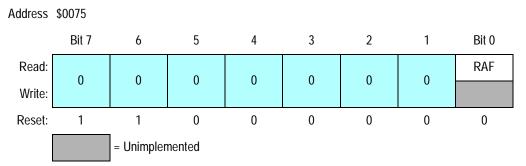

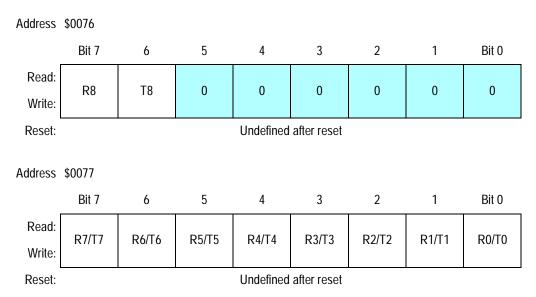

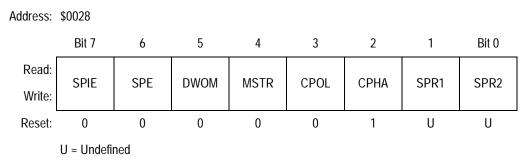

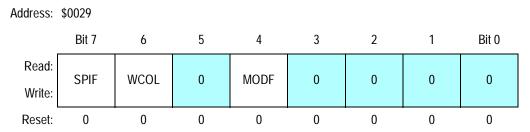

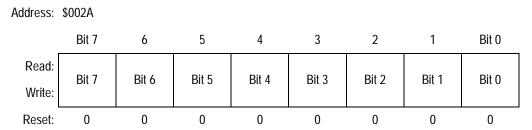

| 8.6<br>8.6.1<br>8.6.2<br>8.6.3<br>8.6.4<br>8.6.5 | SPI Registers173Serial Peripheral Control Register174Serial Peripheral Status Register176Serial Peripheral Data Register177Port D Data Direction Register178System Configuration Options 2179                                     |

|                                                  | Section 9. Timing System                                                                                                                                                                                                          |

| 9.1                                              | Contents                                                                                                                                                                                                                          |

| 9.2                                              | Introduction                                                                                                                                                                                                                      |

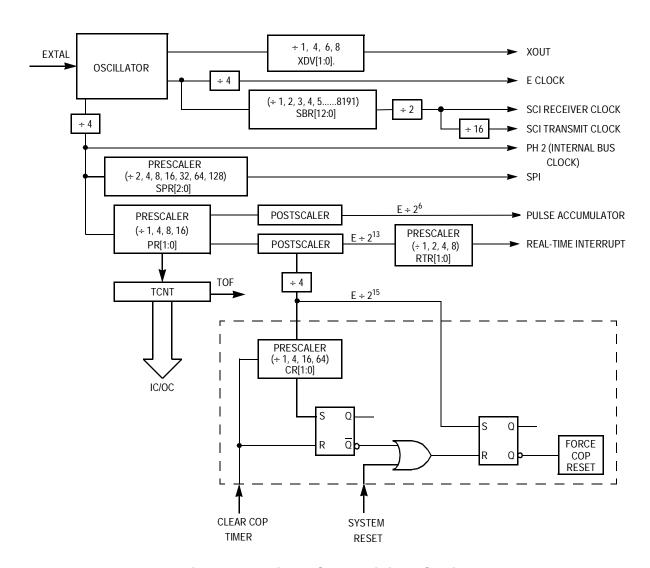

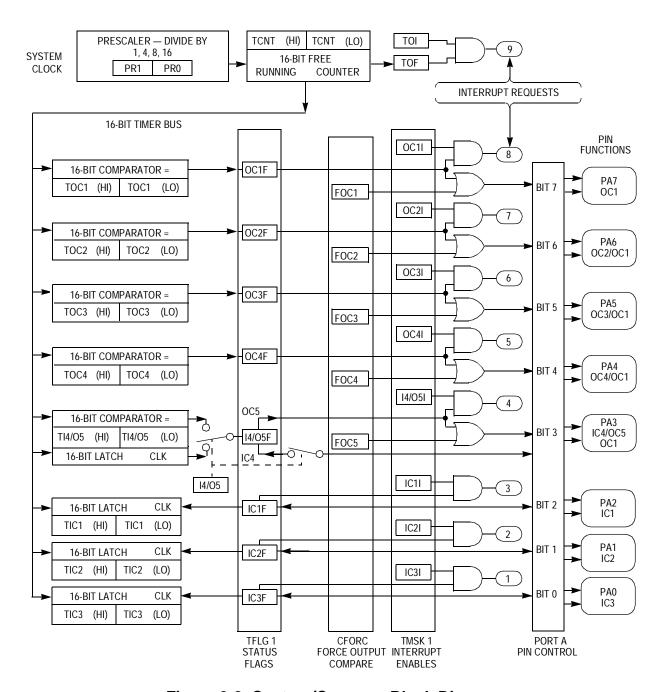

| 9.3                                              | Timer Structure183                                                                                                                                                                                                                |

| 9.4<br>9.4.1<br>9.4.2<br>9.4.3<br>9.4.4          | Input Capture and Output Compare Overview                                                                                                                                                                                         |

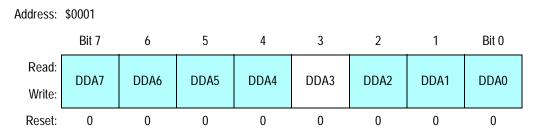

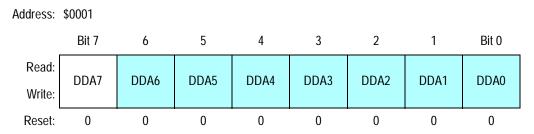

| 9.4.4                                            | Port A Data Direction Register                                                                                                                                                                                                    |

| 9.5    | Input Capture (IC)191                               |

|--------|-----------------------------------------------------|

| 9.5.1  | Timer Input Capture Registers                       |

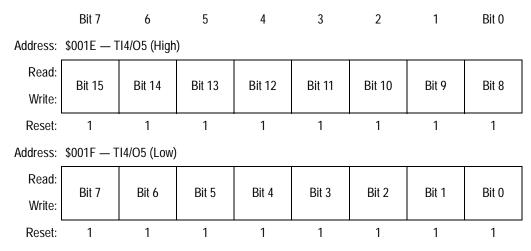

| 9.5.2  | Timer Input Capture 4/Output Compare 5 Register 193 |

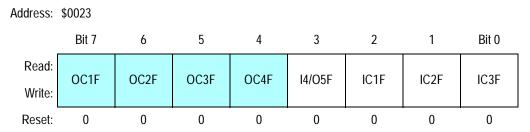

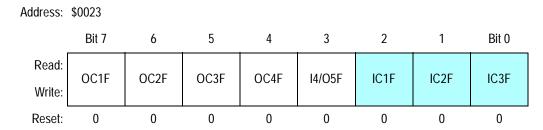

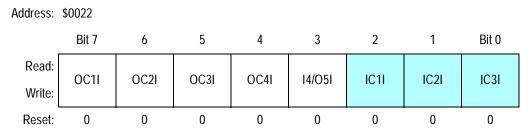

| 9.5.3  | Timer Interrupt Flag 1 Register194                  |

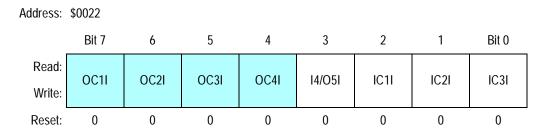

| 9.5.4  | Timer Interrupt Mask 1 Register194                  |

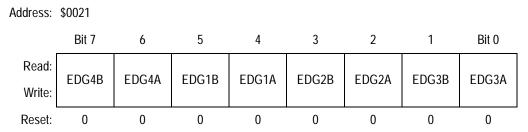

| 9.5.5  | Timer Control 2 Register                            |

| 9.6    | Output Compare (OC)                                 |

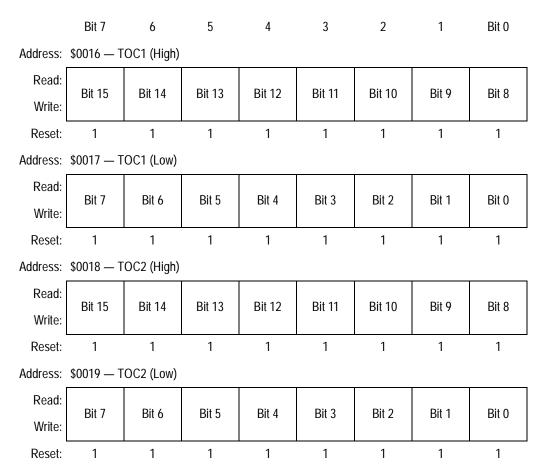

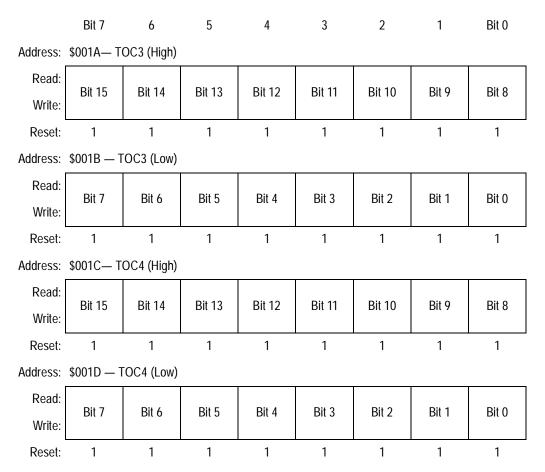

| 9.6.1  | Timer Output Compare Registers197                   |

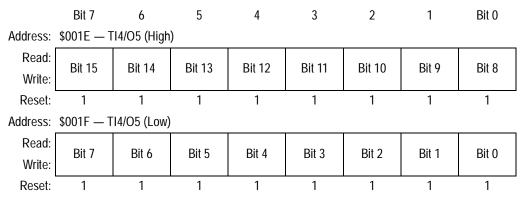

| 9.6.2  | Timer Input Capture 4/Output Compare 5 Register 199 |

| 9.6.3  | Timer Interrupt Flag 1 Register199                  |

| 9.6.4  | Timer Interrupt Mask 1 Register200                  |

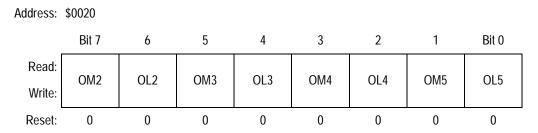

| 9.6.5  | Timer Control 1 Register                            |

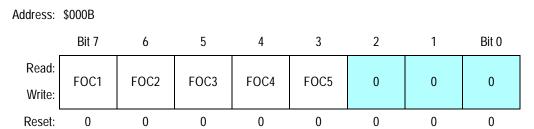

| 9.6.6  | Timer Compare Force Register                        |

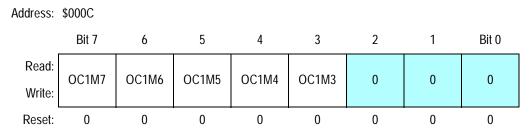

| 9.6.7  | Output Compare 1 Mask Register                      |

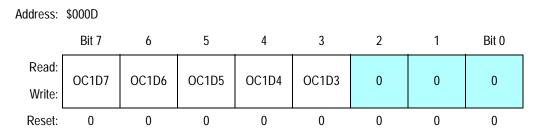

| 9.6.8  | Output Compare 1 Data Register202                   |

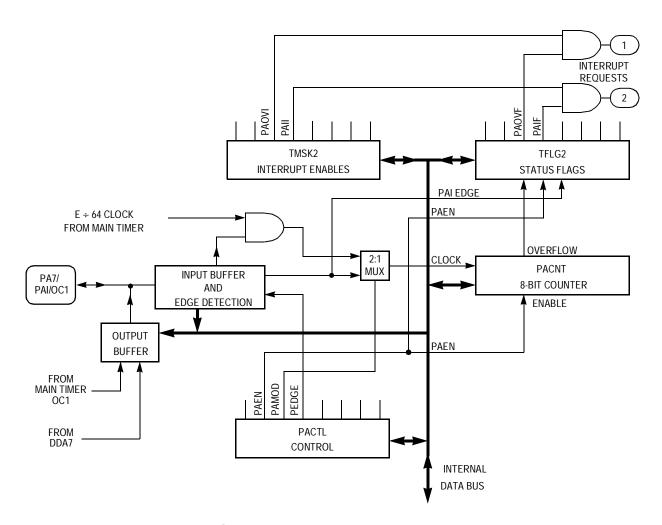

| 9.7    | Pulse Accumulator (PA)                              |

| 9.7.1  | Port A Data Direction Register                      |

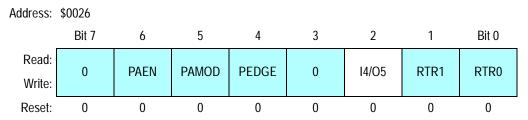

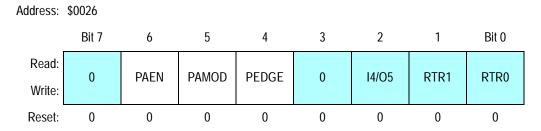

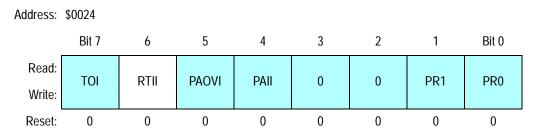

| 9.7.2  | Pulse Accumulator Control Register205               |

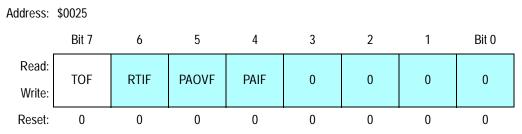

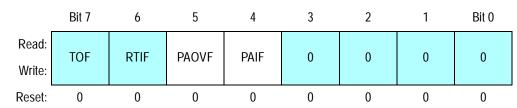

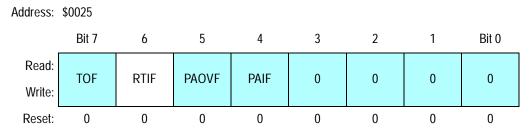

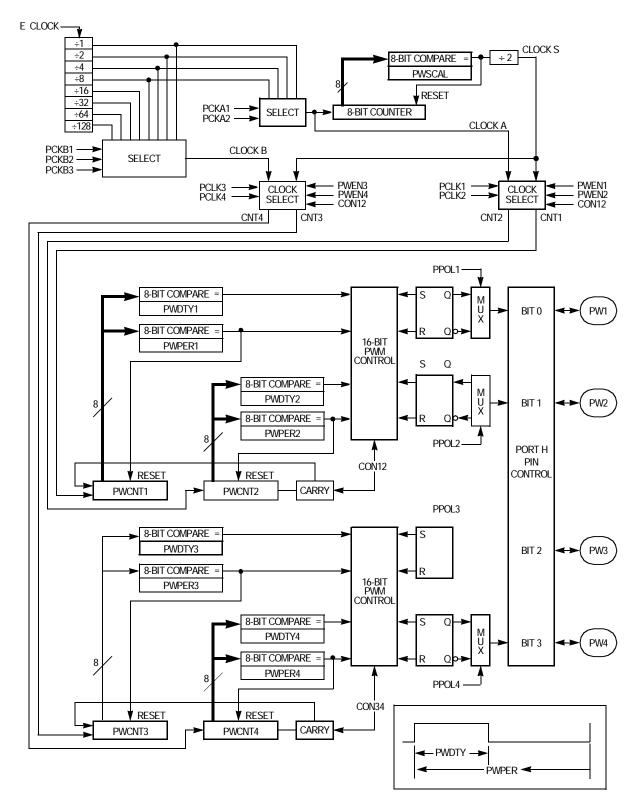

| 9.7.3  | Timer Interrupt Flag 2 Register206                  |

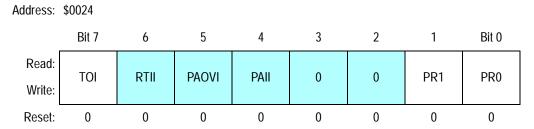

| 9.7.4  | Timer Interrupt Mask 2 Register207                  |

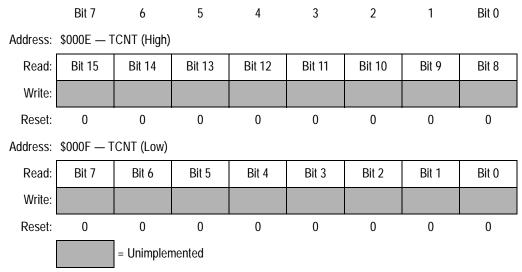

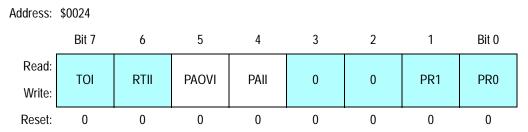

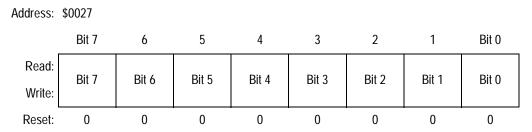

| 9.7.5  | Pulse Accumulator Count Register                    |

| 9.8    | Real-Time Interrupt (RTI)                           |

| 9.8.1  | Timer Interrupt Flag 2 Register209                  |

| 9.8.2  | Timer Interrupt Mask 2 Register209                  |

| 9.8.3  | Pulse Accumulator Control Register210               |

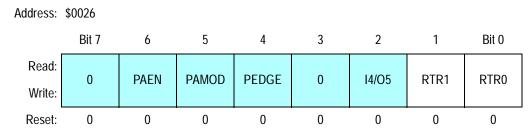

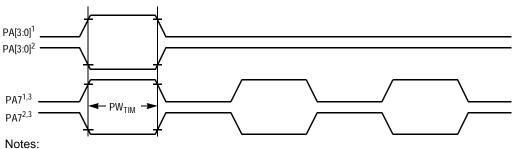

| 9.9    | Pulse-Width Modulator (PWM)                         |

| 9.9.1  | PWM System Description211                           |

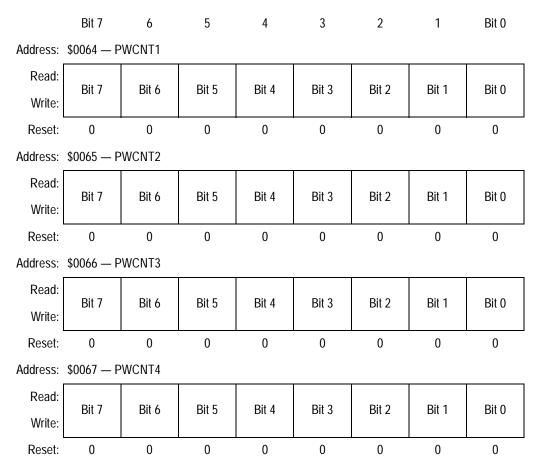

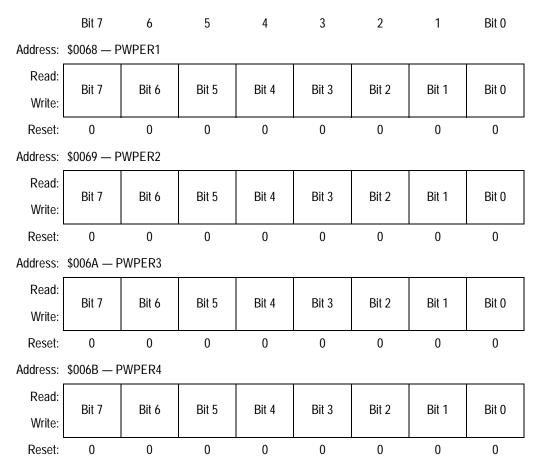

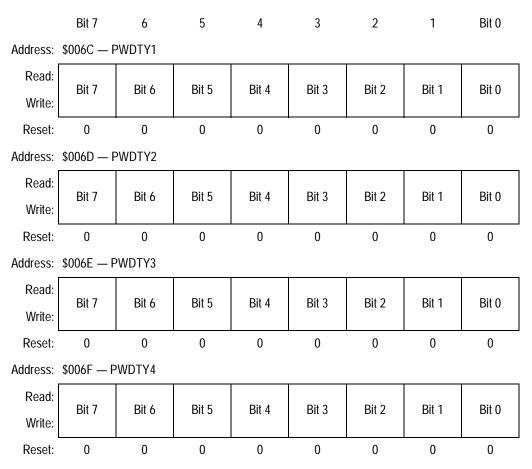

| 9.9.2  | Pulse-Width Modulation Control Registers213         |

| 9.9.2. | Pulse-Width Modulation Timer Clock                  |

|        | Select Register                                     |

| 9.9.2. |                                                     |

| 9.9.2. |                                                     |

| 9.9.2. | _                                                   |

| 9.9.2. | <del>_</del>                                        |

|        | Counters 1 to 4 Registers                           |

# **Table of Contents**

| 11.4   | Chip Selects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 238 |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 11.4.1 | <b> </b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 240 |

| 11.4.2 | haraca de la casa de l |     |

| 11.4.3 | and the second of the second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| 11.4.3 | and the second s |     |

| 11.4.3 | 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| 11.4.3 | and a second and a second a second a second as a secon |     |

| 11.4.3 | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| 11.4.3 | 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| 11.4.4 | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| 11.4.4 | and the second s |     |

| 11.4.4 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 11.4.5 | Clock Stretching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 248 |

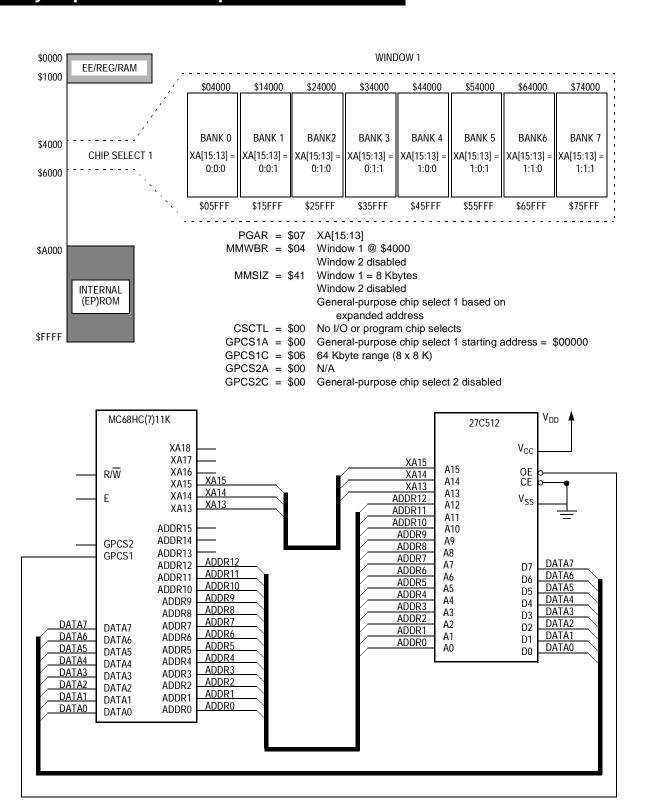

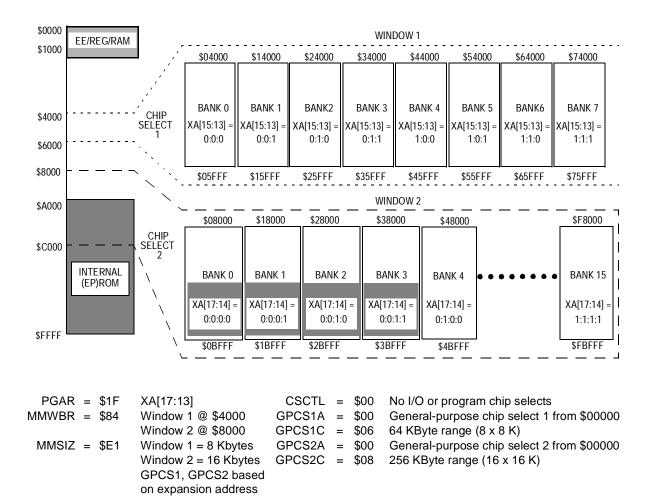

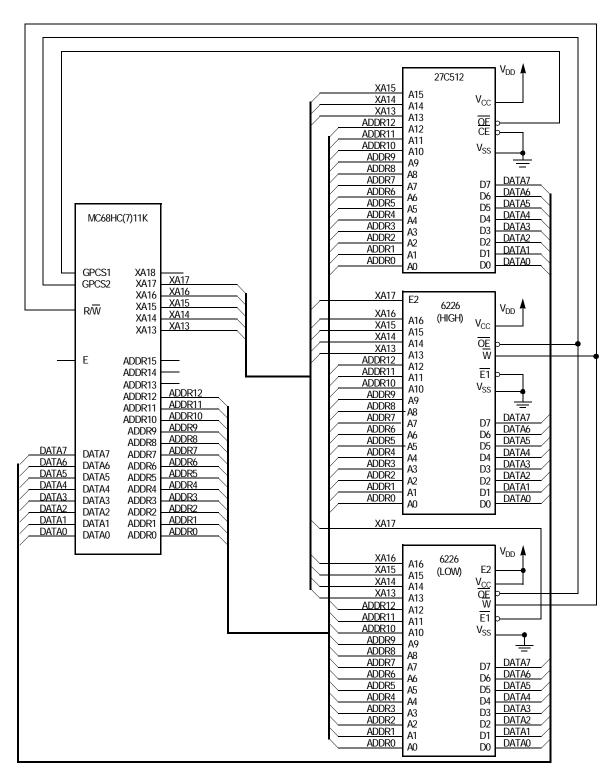

| 11.5   | Memory Expansion Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 249 |

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|        | Section 12. Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| 12.1   | Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 253 |

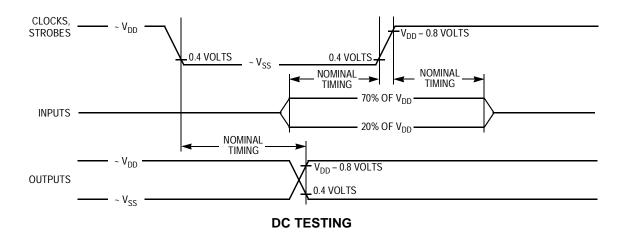

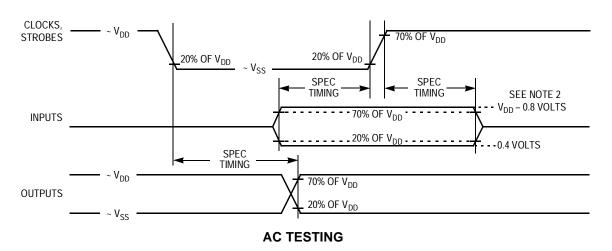

| 12.2   | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 254 |

| 12.3   | Maximum Ratings for Standard Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 254 |

| 12.4   | Functional Operating Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 255 |

| 12.5   | Thermal Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 255 |

| 12.6   | Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 256 |

| 12.7   | Power Dissipation Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 257 |

| 12.8   | Control Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 259 |

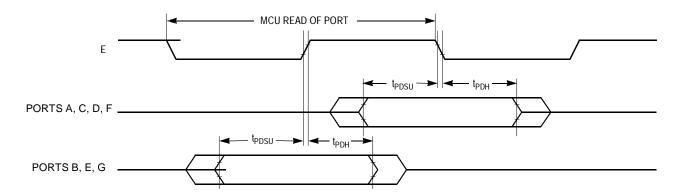

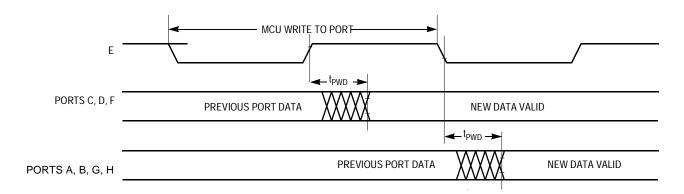

| 12.9   | Peripheral Port Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 263 |

| 12.10  | Analog-to-Digital Converter Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 265 |

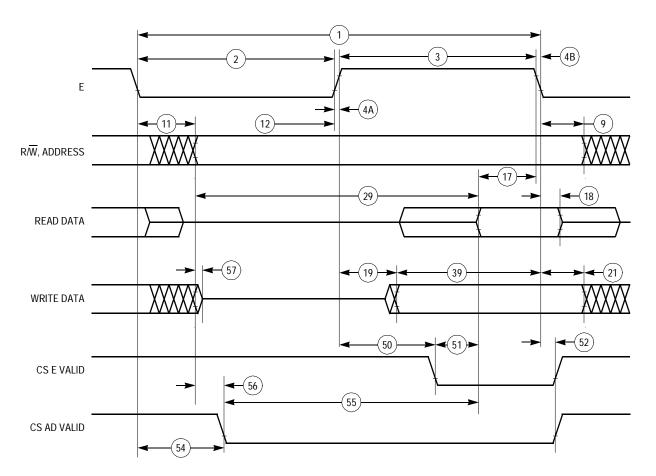

| 12.11  | Expansion Bus Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 267 |

| 12.12  | Serial Peripheral Interface Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 269 |

| 12 13  | FEPROM Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 272 |

# **Table of Contents**

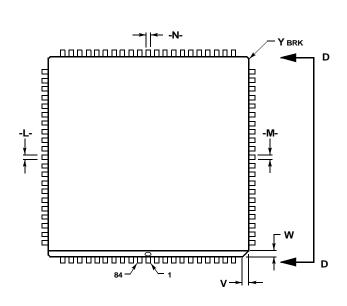

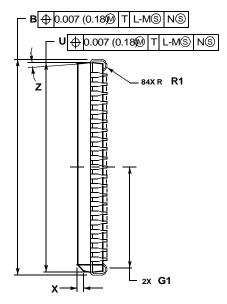

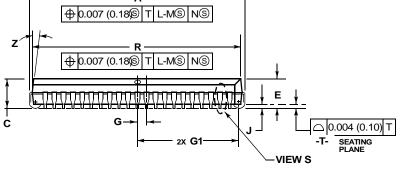

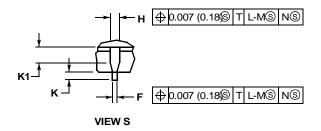

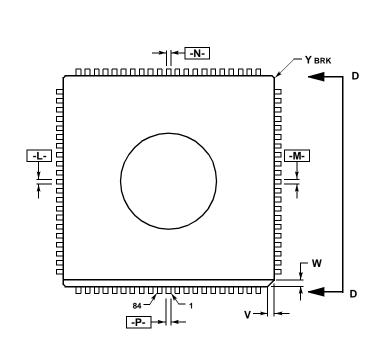

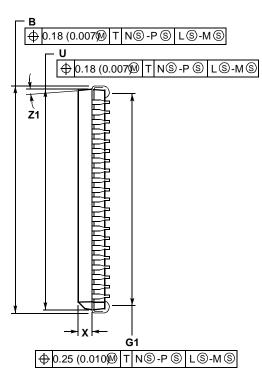

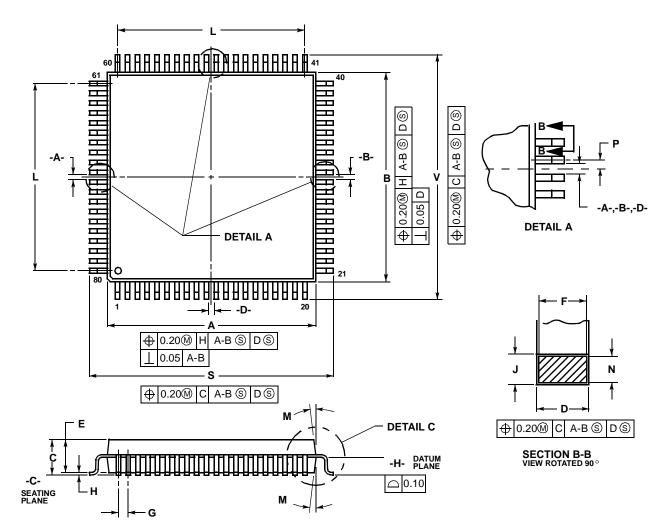

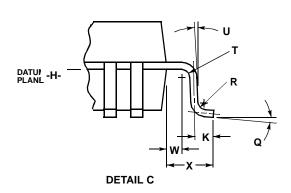

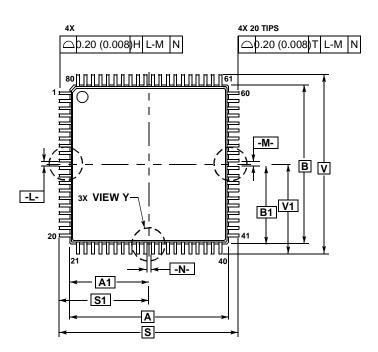

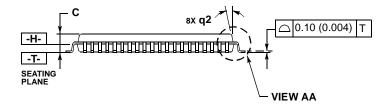

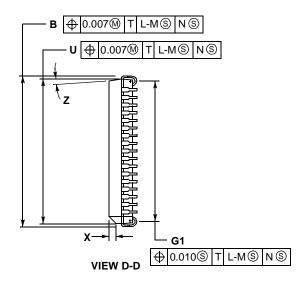

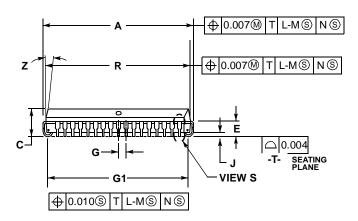

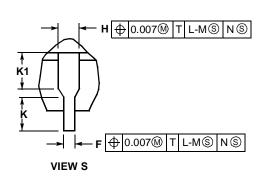

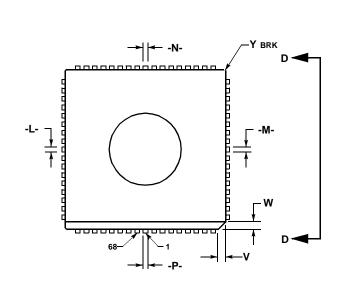

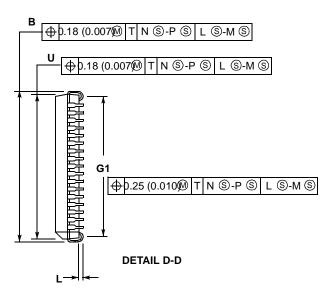

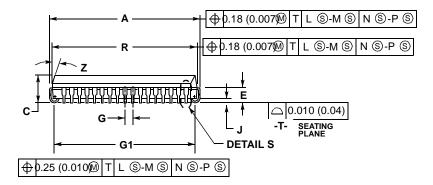

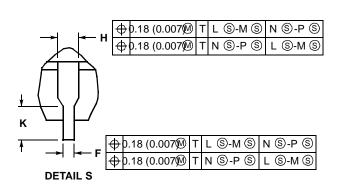

| Section | 13. | Mechanica  | <b>I Data</b> |

|---------|-----|------------|---------------|

| OCCHOIL |     | Micondinoa | ı Data        |

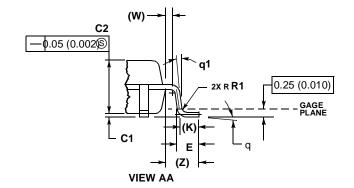

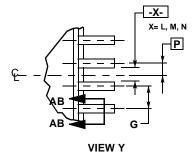

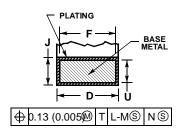

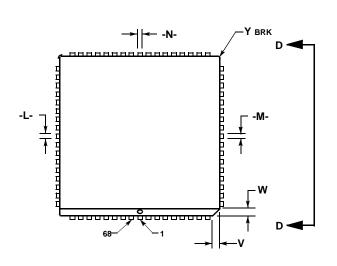

| 13.1 | Contents                                      |

|------|-----------------------------------------------|

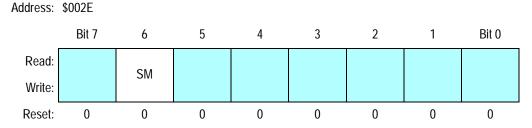

| 13.2 | Introduction                                  |