# Ultra-Small, Octal-Channel, 8-/10-/12-Bit Buffered Output DACs with Internal Reference and SPI Interface

### **General Description**

The MAX5723/MAX5724/MAX5725 8-channel, low-power, 8-/10-/12-bit, voltage-output digital-to-analog converters (DACs) include output buffers and an internal 3ppm/°C reference that is selectable to be 2.048V, 2.500V, or 4.096V. The MAX5723/MAX5724/MAX5725 accept a wide supply voltage range of 2.7V to 5.5V with extremely low power (6mW) consumption to accommodate most low-voltage applications. A precision external reference input allows rail-to-rail operation and presents a 100k $\Omega$  (typ) load to an external reference.

The MAX5723/MAX5724/MAX5725 have a fast 50MHz, 4-wire SPI/QSPI™/MICROWIRE/DSP-compatible serial interface that operates at clock rates up to 50MHz. The DAC output is buffered and has a low supply current of less than 250µA per channel and a low offset error of ±0.5mV (typ). On power-up, the MAX5723/MAX5724/ MAX5725 reset the DAC outputs to zero or midscale based on the status of M/Z logic input, providing flexibility for a variety of control applications. The internal reference is initially powered down to allow use of an external reference. The MAX5723/MAX5724/MAX5725 allow simultaneous output updates using software LOAD commands or the hardware load DAC logic input (LDAC).

The MAX5723/MAX5724/MAX5725 feature a programmable watchdog function which can be enabled to monitor the I/O interface for activity and integrity.

A clear logic input (CLR) allows the contents of the CODE and the DAC registers to be cleared asynchronously and simultaneously sets the DAC outputs to the programmable default value. The MAX5723/MAX5724/MAX5725 are available in a 20-pin TSSOP and an ultra-small, 20-bump WLP package and are specified over the -40°C to +125°C temperature range.

### **Applications**

Programmable Voltage and Current Sources Gain and Offset Adjustment Automatic Tuning and Optical Control Power Amplifier Control and Biasing Process Control and Servo Loops Portable Instrumentation

QSPI is a trademark of Motorola, Inc.

µMAX is a registered trademark of Maxim Integrated Products, Inc.

### **Benefits and Features**

- Eight High-Accuracy DAC Channels

- 12-Bit Accuracy Without Adjustment

- ±1 LSB INL Buffered Voltage Output

- Guaranteed Monotonic Over All Operating Conditions

- Independent Mode Settings for Each DAC

- Three Precision Selectable Internal References

2.048V, 2.500V, or 4.096V

- Internal Output Buffer

- Rail-to-Rail Operation with External Reference

4.5µs Settling Time

- Outputs Directly Drive 2kΩ Loads

- Small 6.5mm x 4.4mm 20-Pin TSSOP or Ultra-Small 2.5mm x 2.3mm 20-Bump WLP Package

- Wide 2.7V to 5.5V Supply Range

- Separate 1.8V to 5.5V V<sub>DDIO</sub> Power-Supply Input

- Fast 50MHz 4-Wire SPI/QSPI/MICROWIRE/DSP-Compatible Serial Interface

- Programmable Interface Watchdog Timer

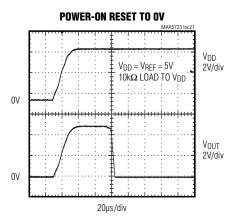

- Pin-Selectable Power-On-Reset to Zero-Scale or Midscale DAC Output

- **LDAC** and **CLR** for Asynchronous DAC Control

- Three Selectable Power-Down Output Impedances

1kΩ, 100kΩ, or High Impedance

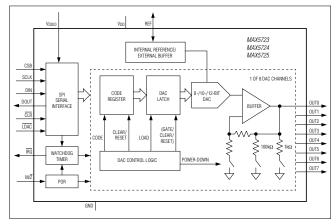

## **Functional Diagram**

Ordering Information appears at end of data sheet.

# Ultra-Small, Octal-Channel, 8-/10-/12-Bit Buffered Output DACs with Internal Reference and SPI Interface

### **Absolute Maximum Ratings**

| V <sub>DD.</sub> V <sub>DDIO</sub> to GND  | 0.3V to +6V                       |

|--------------------------------------------|-----------------------------------|

| OUT_, REF to GND                           | 0.3V to the lower of              |

|                                            | (V <sub>DD</sub> + 0.3V) and +6V  |

| SCLK, CSB, IRQ, M/Z, LDAC, CLR to G        | ND0.3V to +6V                     |

| DIN, DOUT to GND                           | 0.3V to the lower of              |

| ()                                         | V <sub>DDIO</sub> + 0.3V) and +6V |

| Continuous Power Dissipation ( $T_A = +70$ | D°C)                              |

| TSSOP (derate at 13.6mW/°C above 1         | 70°C)1084mW                       |

| WLP (derate at 21.3mW/°C above 70°         | °C)1700mW                         |

| Maximum Continuous Current into Any Pin         | ±50mA        |

|-------------------------------------------------|--------------|

| Operating Temperature40                         | °C to +125°C |

| Storage Temperature65                           | °C to +150°C |

| Lead Temperature (TSSOP only) (soldering, 10s). | +300°C       |

| Soldering Temperature (reflow)                  | +260°C       |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### Package Thermal Characteristics (Note 1)

| TSSOP                                                             | WLP                                                       |

|-------------------------------------------------------------------|-----------------------------------------------------------|

| Junction-to-Ambient Thermal Resistance (θ <sub>JA</sub> )73.8°C/W | Junction-to-Ambient Thermal Resistance (θ <sub>JA</sub> ) |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> )20°C/W      | (Note 2)47°C/W                                            |

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/thermal-tutorial</u>.

Note 2: Visit www.maximintegrated.com/app-notes/index.mvp/id/1891 for information about the thermal performance of WLP packaging.

### **Electrical Characteristics**

(V<sub>DD</sub> = 2.7V to 5.5V, V<sub>DDIO</sub> = 1.8V to 5.5V, V<sub>GND</sub> = 0V, C<sub>L</sub> = 200pF, R<sub>L</sub> = 2k $\Omega$ , T<sub>A</sub> = -40°C to +125°C, unless otherwise noted.) (Note 3)

| PARAMETER                          | SYMBOL | CONDITIONS                       | MIN   | ТҮР   | MAX   | UNITS           |  |  |  |

|------------------------------------|--------|----------------------------------|-------|-------|-------|-----------------|--|--|--|

| DC PERFORMANCE (Note 4)            |        | ·                                |       |       |       |                 |  |  |  |

|                                    |        | MAX5723                          | 8     |       |       |                 |  |  |  |

| Resolution and Monotonicity        | N      | MAX5724                          | 10    |       |       | Bits            |  |  |  |

|                                    |        | MAX5725                          | 12    |       |       |                 |  |  |  |

|                                    |        | MAX5723                          | -0.25 | ±0.05 | +0.25 |                 |  |  |  |

| Integral Nonlinearity (Note 5)     | INL    | MAX5724                          | -0.5  | ±0.2  | +0.5  | LSB             |  |  |  |

|                                    |        | MAX5725                          | -1    | ±0.5  | +1    |                 |  |  |  |

|                                    | DNL    | MAX5723                          | -0.25 | ±0.05 | +0.25 |                 |  |  |  |

| Differential Nonlinearity (Note 5) |        | MAX5724                          | -0.5  | ±0.1  | +0.5  | LSB             |  |  |  |

|                                    |        | MAX5725                          | -1    | ±0.2  | +1    |                 |  |  |  |

| Offset Error (Note 6)              | OE     |                                  | -5    | ±0.5  | +5    | mV              |  |  |  |

| Offset Error Drift                 |        |                                  |       | ±10   |       | µV/°C           |  |  |  |

| Gain Error (Note 6)                | GE     |                                  | -1.0  | ±0.1  | +1.0  | %FS             |  |  |  |

| Gain Temperature Coefficient       |        | With respect to V <sub>REF</sub> |       | ±3.0  |       | ppm of<br>FS/°C |  |  |  |

# Ultra-Small, Octal-Channel, 8-/10-/12-Bit Buffered Output DACs with Internal Reference and SPI Interface

## **Electrical Characteristics (continued)**

(V\_DD = 2.7V to 5.5V, V\_DDIO = 1.8V to 5.5V, V\_GND = 0V, C\_L = 200pF, R\_L = 2k\Omega, T\_A = -40^{\circ}C to +125°C, unless otherwise noted.) (Note 3)

| PARAMETER                           | SYMBOL | C                                   | ONDITIONS                                       | MIN  | TYP  | MAX                      | UNITS |

|-------------------------------------|--------|-------------------------------------|-------------------------------------------------|------|------|--------------------------|-------|

| Zero-Scale Error                    |        |                                     |                                                 | 0    |      | +10                      | mV    |

| Full-Scale Error                    |        | With respect to V                   | REF                                             | -0.5 |      | +0.5                     | %FS   |

| DAC OUTPUT CHARACTERIST             | rics   |                                     |                                                 |      |      |                          |       |

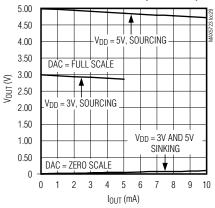

|                                     |        | No load                             |                                                 | 0    |      | $V_{DD}$                 |       |

| Output Voltage Range (Note 7)       |        | $2k\Omega$ load to GND              |                                                 | 0    |      | V <sub>DD</sub> -<br>0.2 | V     |

|                                     |        | 2k $\Omega$ load to V <sub>DD</sub> |                                                 | 0.2  |      | V <sub>DD</sub>          |       |

|                                     |        |                                     | $V_{DD} = 3V \pm 10\%,$<br>$II_{OUT}I \le 5mA$  |      | 300  |                          |       |

| Load Regulation                     |        | $V_{OUT} = V_{FS}/2$                | $V_{DD} = 5V \pm 10\%,$<br>$ I_{OUT}  \le 10mA$ |      | 300  |                          | μV/mA |

|                                     |        |                                     | $V_{DD} = 3V \pm 10\%,$<br>$II_{OUT}I \le 5mA$  |      | 0.3  |                          | Ω     |

| DC Output Impedance                 |        | $V_{OUT} = V_{FS}/2$                | $V_{DD} = 5V \pm 10\%,$<br>$ I_{OUT}  \le 10mA$ | 0.3  |      |                          | 22    |

| Maximum Capacitive Load<br>Handling | CL     |                                     |                                                 |      | 500  |                          | pF    |

| Resistive Load Handling             | RL     |                                     |                                                 | 2    |      |                          | kΩ    |

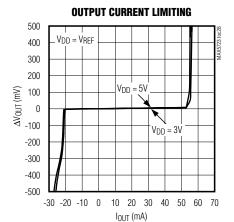

|                                     |        |                                     | Sourcing (output shorted to GND)                | 30   |      |                          | ٣٨    |

| Short-Circuit Output Current        |        | V <sub>DD</sub> = 5.5V              | Sinking (output shorted to $V_{DD}$ )           |      | 50   |                          | - mA  |

| DC Power-Supply Rejection           |        | $V_{DD} = 3V \pm 10\%$              | or 5V ±10%                                      |      | 100  |                          | μV/V  |

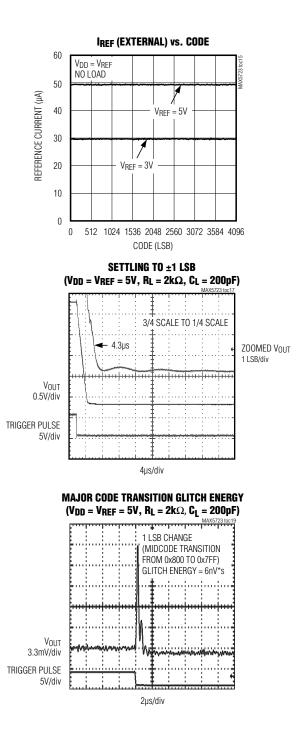

| DYNAMIC PERFORMANCE                 |        |                                     |                                                 |      |      |                          |       |

| Voltage-Output Slew Rate            | SR     | Positive and neg                    | ative                                           |      | 1.0  |                          | V/µs  |

|                                     |        | 1/4 scale to 3/4 sca                | ale, to $\leq$ 1 LSB, MAX5723                   |      | 2.2  |                          |       |

| Voltage-Output Settling Time        |        | 1/4 scale to 3/4 sca                | ale, to $\leq$ 1 LSB, MAX5724                   |      | 2.6  |                          | μs    |

|                                     |        | 1/4 scale to 3/4 sca                | ale, to $\leq$ 1 LSB, MAX5725                   |      | 4.5  |                          |       |

| DAC Glitch Impulse                  |        | Major code trans                    | sition (code x7FF to x800)                      |      | 7    |                          | nV*s  |

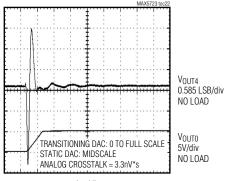

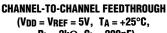

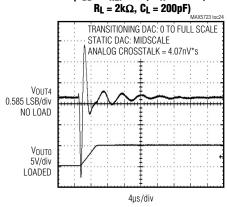

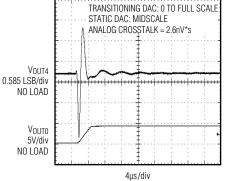

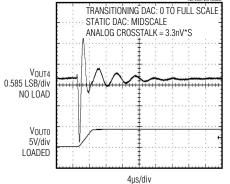

| Channel-to-Channel                  |        | Internal reference                  | e                                               |      | 3.3  |                          |       |

| Feedthrough (Note 8)                |        | External reference                  |                                                 |      | 4.07 |                          | nV*s  |

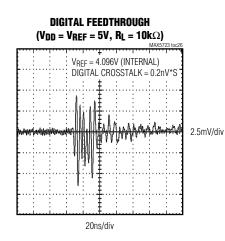

| Digital Feedthrough                 |        | Midscale code, a                    | all digital inputs from 0V to                   |      | 0.2  |                          | nV*s  |

| Power-Up Time                       |        | Startup calibration                 | on time (Note 9)                                |      | 200  |                          | μs    |

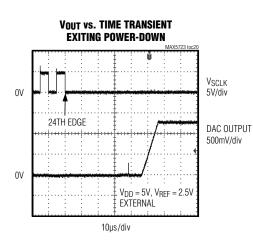

| rower-up nime                       |        | From power-dov                      | /n                                              |      | 50   |                          | μs    |

# Ultra-Small, Octal-Channel, 8-/10-/12-Bit Buffered Output DACs with Internal Reference and SPI Interface

## **Electrical Characteristics (continued)**

(V\_DD = 2.7V to 5.5V, V\_DDIO = 1.8V to 5.5V, V\_GND = 0V, C\_L = 200pF, R\_L = 2k\Omega, T\_A = -40^{\circ}C to +125°C, unless otherwise noted.) (Note 3)

| PARAMETER                    | SYMBOL | CON                       | IDITIONS             | MIN | ТҮР | MAX | UNITS                  |  |  |

|------------------------------|--------|---------------------------|----------------------|-----|-----|-----|------------------------|--|--|

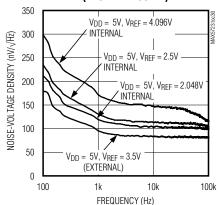

|                              |        | External reference        | f = 1kHz             |     | 90  |     |                        |  |  |

|                              |        | External reference        | f = 10kHz            |     | 82  |     | 1                      |  |  |

|                              |        | 2.048V internal           | f = 1kHz             |     | 112 |     | 1                      |  |  |

| Output Voltage-Noise Density |        | reference                 | f = 10 kHz           |     | 102 |     |                        |  |  |

| (DAC Output at Midscale)     |        | 2.5V internal             | f = 1kHz             |     | 125 |     | nV/√Hz                 |  |  |

|                              |        | reference                 | f = 10 kHz           |     | 110 |     | 1                      |  |  |

|                              |        | 4.096V internal           | f = 1kHz             |     | 160 |     | 1                      |  |  |

|                              |        | reference                 | f = 10 kHz           |     | 145 |     |                        |  |  |

|                              |        |                           | f = 0.1Hz to 10Hz    |     | 12  |     |                        |  |  |

|                              |        | External reference        | f = 0.1Hz to $10kHz$ |     | 76  |     | ]                      |  |  |

|                              |        |                           | f = 0.1Hz to 300kHz  |     | 385 |     | 1                      |  |  |

|                              |        |                           | f = 0.1Hz to 10Hz    |     | 14  |     | 1                      |  |  |

|                              |        | 2.048V internal reference | f = 0.1Hz to $10kHz$ |     | 91  |     | 1                      |  |  |

| Integrated Output Noise      |        | Telefence                 | f = 0.1Hz to 300kHz  |     | 450 |     |                        |  |  |

| (DAC Output at Midscale)     |        |                           | f = 0.1Hz to 10Hz    |     | 15  |     | - μV <sub>P-P</sub>    |  |  |

|                              |        | 2.5V internal reference   | f = 0.1Hz to 10kHz   |     | 99  |     | -                      |  |  |

|                              |        | Telefelice                | f = 0.1Hz to 300kHz  |     | 470 |     |                        |  |  |

|                              |        | 4.0001/11                 | f = 0.1Hz to 10Hz    |     | 16  |     |                        |  |  |

|                              |        | 4.096V internal reference | f = 0.1Hz to $10kHz$ |     | 124 |     |                        |  |  |

|                              |        | relefence                 | f = 0.1Hz to 300kHz  |     | 490 |     |                        |  |  |

|                              |        | External reference        | f = 1kHz             |     | 114 |     |                        |  |  |

|                              |        | External reference        | f = 10 kHz           |     | 99  |     | <sup> </sup>           |  |  |

|                              |        | 2.048V internal           | f = 1kHz             |     | 175 |     | nV/√Hz                 |  |  |

| Output Voltage-Noise Density |        | reference                 | f = 10 kHz           |     | 153 |     |                        |  |  |

| (DAC Output at Full Scale)   |        | 2.5V internal             | f = 1kHz             |     | 200 |     |                        |  |  |

|                              |        | reference                 | f = 10 kHz           |     | 174 |     |                        |  |  |

|                              |        | 4.096V internal           | f = 1kHz             |     | 295 |     |                        |  |  |

|                              |        | reference                 | f = 10 kHz           |     | 255 |     |                        |  |  |

|                              |        |                           | f = 0.1Hz to 10Hz    |     | 13  |     |                        |  |  |

|                              |        | External reference        | f = 0.1Hz to $10kHz$ |     | 94  |     | ]                      |  |  |

|                              |        |                           | f = 0.1Hz to 300kHz  |     | 540 |     | 1                      |  |  |

|                              |        |                           | f = 0.1Hz to 10Hz    |     | 19  |     | ]                      |  |  |

|                              |        | 2.048V internal reference | f = 0.1Hz to $10kHz$ |     | 143 |     | -<br>μV <sub>P-P</sub> |  |  |

| Integrated Output Noise      |        |                           | f = 0.1Hz to 300kHz  |     | 685 |     |                        |  |  |

| (DAC Output at Full Scale)   |        |                           | f = 0.1Hz to 10Hz    |     | 21  |     |                        |  |  |

|                              |        | 2.5V internal reference   | f = 0.1Hz to $10kHz$ |     | 159 |     |                        |  |  |

|                              |        |                           | f = 0.1Hz to 300kHz  |     | 705 |     |                        |  |  |

|                              |        |                           | f = 0.1Hz to 10Hz    |     | 26  |     | 1                      |  |  |

|                              |        | 4.096V internal           | f = 0.1Hz to $10kHz$ |     | 213 |     | 1                      |  |  |

|                              |        | reference                 | f = 0.1Hz to 300kHz  | 1   | 750 |     | 1                      |  |  |

# Ultra-Small, Octal-Channel, 8-/10-/12-Bit Buffered Output DACs with Internal Reference and SPI Interface

# **Electrical Characteristics (continued)**

(V\_DD = 2.7V to 5.5V, V\_DDIO = 1.8V to 5.5V, V\_GND = 0V, C\_L = 200pF, R\_L = 2k\Omega, T\_A = -40^{\circ}C to +125°C, unless otherwise noted.) (Note 3)

| PARAMETER                             | SYMBOL            | CONE                                                            | DITIONS                                              | MIN   | ΤΥΡ   | MAX             | UNITS  |  |

|---------------------------------------|-------------------|-----------------------------------------------------------------|------------------------------------------------------|-------|-------|-----------------|--------|--|

| REFERENCE INPUT                       |                   |                                                                 |                                                      |       |       |                 |        |  |

| Reference Input Range                 | V <sub>REF</sub>  |                                                                 |                                                      | 1.24  |       | V <sub>DD</sub> | V      |  |

| Reference Input Current               | I <sub>REF</sub>  | $V_{\text{REF}} = V_{\text{DD}} = 5.5 \text{V}$                 |                                                      |       | 55    | 74              | μA     |  |

| Reference Input Impedance             | R <sub>REF</sub>  |                                                                 |                                                      | 75    | 100   |                 | kΩ     |  |

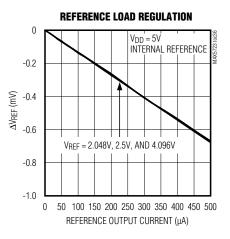

| REFERENCE OUTPUT                      |                   |                                                                 |                                                      |       |       |                 |        |  |

|                                       |                   | V <sub>REF</sub> = 2.048V, T <sub>A</sub> =                     | +25°C                                                | 2.043 | 2.048 | 2.053           |        |  |

| Reference Output Voltage              | V <sub>REF</sub>  | $V_{REF} = 2.5V, T_A = +$                                       | 25°C                                                 | 2.494 | 2.500 | 2.506           | V      |  |

|                                       |                   | $V_{REF} = 4.096V, T_{A} =$                                     | +25°C                                                | 4.086 | 4.096 | 4.106           |        |  |

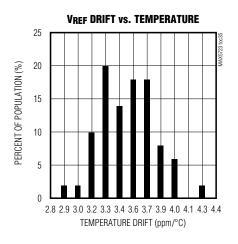

| Reference Temperature                 |                   | MAX5725A                                                        |                                                      |       | ±3    | ±10             | ppm/°C |  |

| Coefficient (Note 10)                 |                   | MAX5723/MAX5724,                                                | /MAX5725B                                            |       | ±10   | ±25             |        |  |

| Reference Drive Capacity              | _                 | External load                                                   |                                                      |       | 25    |                 | kΩ     |  |

| Reference Capacitive Load<br>Handling |                   |                                                                 |                                                      | 200   |       | pF              |        |  |

| Reference Load Regulation             |                   | I <sub>SOURCE</sub> = 0 to 500                                  | A                                                    |       | 2     |                 | mV/mA  |  |

| Reference Line Regulation             |                   |                                                                 |                                                      | 0.05  | -     | mV/V            |        |  |

| POWER REQUIREMENTS                    |                   | - <b>-</b>                                                      |                                                      |       |       |                 | 1      |  |

|                                       |                   | $V_{REF} = 4.096V$                                              |                                                      | 4.5   |       | 5.5             | v      |  |

| Supply Voltage                        | V <sub>DD</sub>   | All other options                                               |                                                      | 2.7   |       | 5.5             | v      |  |

| I/O Supply Voltage                    | V <sub>DDIO</sub> |                                                                 |                                                      | 1.8   |       | 5.5             | V      |  |

|                                       |                   |                                                                 | $V_{REF} = 2.048V$                                   |       | 1.6   | 2               |        |  |

|                                       |                   | Internal reference                                              | $V_{\text{REF}} = 2.5 V$                             |       | 1.7   | 2.1             |        |  |

| Supply Current (Note 11)              | I <sub>DD</sub>   |                                                                 | $V_{\text{REF}} = 4.096V$                            |       | 2.0   | 2.5             | mA     |  |

|                                       |                   |                                                                 | $V_{\text{REF}} = 3V$                                |       | 1.6   | 2.0             |        |  |

|                                       |                   | External reference                                              | $V_{\text{REF}} = 5V$                                |       | 1.9   | 2.5             | 1      |  |

|                                       |                   | All DACs off, interna                                           |                                                      |       | 140   |                 |        |  |

| Power-Down Mode Supply                | I <sub>PD</sub>   | All DACs off, interna<br>$T_A = -40^{\circ}C$ to $+85^{\circ}C$ | l reference OFF,                                     |       | 0.7   | 2               | μA     |  |

| Current                               |                   | All DACs off, interna<br>$T_A = +125^{\circ}C$                  |                                                      | 2     | 4     | -               |        |  |

| Digital Supply Current                | I <sub>DDIO</sub> | Static logic inputs, a                                          |                                                      |       | 1     | μA              |        |  |

| DIGITAL INPUT CHARACTER               | ISTICS (SCLK      | , DIN, CSB, LDAC, CI                                            |                                                      |       |       |                 | 1      |  |

| Input Leakage Current                 | I <sub>IN</sub>   | V <sub>IN</sub> = 0V or V <sub>DDIO</sub> , a<br>(Note 11)      |                                                      |       | ±0.1  | ±1              | μA     |  |

|                                       |                   | $V_{IN} = 0V \text{ or } V_{DD}, \text{ for}$                   | $V_{IN} = 0V \text{ or } V_{DD}$ , for M/Z (Note 11) |       |       |                 |        |  |

|                                       |                   | · · · · · · · · · · · · · · · · · · ·                           |                                                      |       |       |                 | •      |  |

# Ultra-Small, Octal-Channel, 8-/10-/12-Bit Buffered Output DACs with Internal Reference and SPI Interface

# **Electrical Characteristics (continued)**

(V<sub>DD</sub> = 2.7V to 5.5V, V<sub>DDIO</sub> = 1.8V to 5.5V, V<sub>GND</sub> = 0V, C<sub>L</sub> = 200pF, R<sub>L</sub> = 2k $\Omega$ , T<sub>A</sub> = -40°C to +125°C, unless otherwise noted.) (Note 3)

| PARAMETER                                  | SYMBOL           | CON                                                 | DITIONS                         | MIN                        | ТҮР    | MAX                        | UNITS |

|--------------------------------------------|------------------|-----------------------------------------------------|---------------------------------|----------------------------|--------|----------------------------|-------|

|                                            |                  | (All inputs except                                  | 2.2V < V <sub>DDIO</sub> < 5.5V | 0.7 x<br>V <sub>DDIO</sub> |        |                            | V     |

| Input High Voltage                         | V <sub>IH</sub>  | $M/\overline{Z}$ )                                  | 1.8V < V <sub>DDIO</sub> < 2.2V | 0.8 x<br>V <sub>DDIO</sub> |        |                            | N     |

|                                            |                  | 2.7V < V <sub>DD</sub> < 5.5V                       | (for M/Z)                       | 0.7 x<br>V <sub>DD</sub>   |        |                            | V     |

|                                            |                  | (All inputs except                                  | 2.2V < V <sub>DDIO</sub> < 5.5V |                            |        | 0.3 x<br>V <sub>DDIO</sub> | V     |

| Input Low Voltage                          | V <sub>IL</sub>  | M/Z)                                                | 1.8V < V <sub>DDIO</sub> < 2.2V |                            |        | 0.2 x<br>V <sub>DDIO</sub> | V     |

|                                            |                  | 2.7V < V <sub>DD</sub> < 5.5V                       | (for $M/\overline{Z}$ )         |                            |        | 0.3 x<br>V <sub>DD</sub>   | V     |

| Input Capacitance (Note 10)                | C <sub>IN</sub>  |                                                     |                                 |                            |        | 10                         | pF    |

| Hysteresis Voltage                         | V <sub>H</sub>   |                                                     |                                 |                            | 0.15   |                            | V     |

| DIGITAL OUTPUT (IRQ)                       |                  |                                                     |                                 |                            |        |                            |       |

| Output Low Voltage                         | V <sub>OL</sub>  | I <sub>SINK</sub> = 3mA                             |                                 |                            |        | 0.2                        | V     |

| Output Inactive Leakage                    | I <sub>OFF</sub> |                                                     |                                 |                            | ±0.1   | ±1                         | μΑ    |

| Output Inactive Capacitance (Note 10)      | C <sub>OFF</sub> |                                                     |                                 |                            |        | 10                         | pF    |

| DIGITAL OUTPUT (DOUT)                      |                  | · · · · · · · · · · · · · · · · · · ·               |                                 |                            |        |                            |       |

| Output High Voltage                        | Varia            | V <sub>DDIO</sub> > 2.5V, I <sub>SOURCE</sub> = 3mA |                                 | V <sub>DDIO</sub><br>- 0.2 |        |                            | V     |

| Output high voltage                        | V <sub>OH</sub>  | V <sub>DDIO</sub> > 1.8V, I <sub>SOL</sub>          | JRCE = 2mA                      | V <sub>DDIO</sub><br>- 0.2 |        |                            | V     |

| Output Low Voltage                         | V <sub>OL</sub>  | $V_{\text{DDIO}} > 2.5 \text{V}, I_{\text{SINF}}$   | <sub>K</sub> = 3mA              |                            |        | 0.2                        | V     |

| Oulput Low Voltage                         | VOL              | $V_{DDIO} > 1.8V, I_{SINI}$                         | < = 2mA                         |                            |        | 0.2                        | v     |

| Output Short-Circuit Current               | I <sub>OSS</sub> | I <sub>SINK</sub> , I <sub>SOURCE</sub>             |                                 |                            | ±100   |                            | mA    |

| Output Three-State Leakage                 | I <sub>OZ</sub>  |                                                     |                                 |                            | ±0.1   | ±1                         | μA    |

| Output Three-State<br>Capacitance          | C <sub>OZ</sub>  |                                                     |                                 |                            | 10     |                            | рF    |

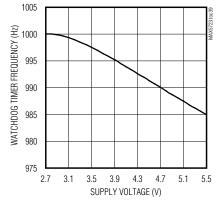

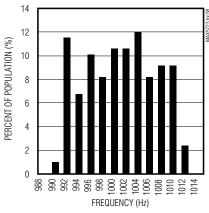

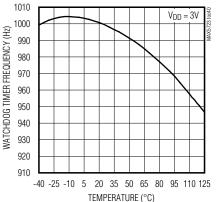

| WATCHDOG TIMER CHARACT                     | ERISTICS         |                                                     |                                 |                            |        |                            | 1     |

| Watchdog Timer Period                      | twdosc           | $V_{DD} = 3V, T_A = +28$                            | 5°C                             | 0.95                       | 1      | 1.05                       | ms    |

| Watchdog Timer Period Supply<br>Drift      |                  | $V_{DD} = 2.7V \text{ to } 5.5V$                    | , T <sub>A</sub> = +25°C        |                            | 0.6    |                            | %/V   |

| Watchdog Timer Period<br>Temperature Drift |                  | V <sub>DD</sub> = 3V                                |                                 |                            | 0.0375 |                            | %/°C  |

# Ultra-Small, Octal-Channel, 8-/10-/12-Bit Buffered Output DACs with Internal Reference and SPI Interface

### **Electrical Characteristics (continued)**

(V<sub>DD</sub> = 2.7V to 5.5V, V<sub>DDIO</sub> = 1.8V to 5.5V, V<sub>GND</sub> = 0V, C<sub>L</sub> = 200pF, R<sub>L</sub> = 2k $\Omega$ , T<sub>A</sub> = -40°C to +125°C, unless otherwise noted.) (Note 3)

| PARAMETER                        | SYMBOL            | CONE                                          | ITIONS                                                     | MIN | TYP | MAX  | UNITS |  |

|----------------------------------|-------------------|-----------------------------------------------|------------------------------------------------------------|-----|-----|------|-------|--|

| SPI TIMING CHARACTERISTIC        | S                 | ·                                             | ·                                                          |     |     |      | ·     |  |

|                                  |                   |                                               | Write mode                                                 | 0   |     | 50   |       |  |

|                                  |                   | 2.7V < V <sub>DDIO</sub> < 5.5V               | Read mode,<br>strobing on 1 SCLK                           | 0   |     | 25   |       |  |

|                                  | f                 |                                               | Read mode,<br>strobing on ½ SCLK                           | 0   |     | 12.5 | MHz   |  |

| SCLK Frequency                   | fsclk             |                                               | Write mode                                                 | 0   |     | 33   |       |  |

|                                  |                   | 1.8V < V <sub>DDIO</sub> < 2.7V               | Read mode,<br>strobing on 1 SCLK                           | 0   |     | 20   |       |  |

|                                  |                   |                                               | Read mode,<br>strobing on ½ SCLK                           | 0   |     | 10   |       |  |

| SCLK Period                      | t                 | $2.7V < V_{DDIO} < 5.5V$                      | 20                                                         |     |     | ns   |       |  |

| SOLK FEIIOU                      | <sup>t</sup> SCLK | $1.8V < V_{DDIO} < 2.7V$                      | $1.8V < V_{DDIO} < 2.7V$ , write mode                      |     |     |      | 115   |  |

| SCLK Pulse Width High            | t <sub>CH</sub>   |                                               |                                                            | 8   |     |      | ns    |  |

| SCLK Pulse Width Low             | t <sub>CL</sub>   |                                               |                                                            | 8   |     |      | ns    |  |

| CSB Fall to SCLK Fall Setup Time | toooo             | To first SCLK falling                         | $2.7\mathrm{V} < \mathrm{V_{DDIO}} < 5.5\mathrm{V}$        | 8   |     |      | ns    |  |

|                                  | tCSS0             | edge                                          | $1.8\mathrm{V} < \mathrm{V}_\mathrm{DDIO} < 2.7\mathrm{V}$ | 12  |     |      | 113   |  |

| CSB Fall to SCLK Fall Hold Time  | tCSH0             | Applies to inactive SC preceding the first SC |                                                            | 0   |     |      | ns    |  |

| CSB Rise to SCLK Fall Hold Time  | t <sub>CSH1</sub> | Applies to the 24th SC                        | CLK falling edge                                           | 0   |     |      | ns    |  |

| CSB Rise to SCLK Fall            | t <sub>CSA</sub>  | Applies to the 24th SC aborted sequence       | CLK falling edge,                                          | 12  |     |      | ns    |  |

| SCLK Fall to CSB Fall            | t <sub>CSF</sub>  | Applies to 24th SCL                           | K falling edge                                             | 100 |     |      | ns    |  |

| CSB Pulse Width High             | t <sub>CSPW</sub> |                                               |                                                            | 20  |     |      | ns    |  |

| DIN to SCLK Fall Setup Time      | t <sub>DS</sub>   |                                               |                                                            | 5   |     |      | ns    |  |

| DIN to SCLK Fall Hold Time       | t <sub>DH</sub>   |                                               |                                                            | 4.5 |     |      | ns    |  |

| CLR Pulse Width Low              | t <sub>CLPW</sub> |                                               |                                                            | 20  |     |      | ns    |  |

| CLR Rise to CSB Fall             | tcsc              | Required for comman                           | nd to be executed                                          | 20  |     |      | ns    |  |

| LDAC Pulse Width Low             | t <sub>LDPW</sub> |                                               |                                                            | 20  |     |      | ns    |  |

| LDAC Fall to SCLK Fall Hold      | t <sub>LDH</sub>  | Applies to 24th SCLK                          | falling edge                                               | 20  |     | _    | ns    |  |

| SCLK Fall to DOUT Transition     | teer              | DPHA = 0,                                     | $2.7\mathrm{V} < \mathrm{V}_\mathrm{DDIO} < 5.5\mathrm{V}$ |     |     | 35   |       |  |

|                                  | <sup>t</sup> dot  | $C_{LOAD} = 20 pF$                            | $1.8\mathrm{V} < \mathrm{V}_\mathrm{DDIO} < 2.7\mathrm{V}$ |     |     | 40   | ns    |  |

| SCLK Rise to DOUT Transition     | tpot              |                                               | $2.7\mathrm{V} < \mathrm{V}_\mathrm{DDIO} < 5.5\mathrm{V}$ |     |     | 35   | ns    |  |

|                                  | t <sub>DOT</sub>  | $C_{LOAD} = 20 pF$                            | 1.8V < V <sub>DDIO</sub> < 2.7V                            |     |     | 40   | 115   |  |

# Ultra-Small, Octal-Channel, 8-/10-/12-Bit Buffered Output DACs with Internal Reference and SPI Interface

### **Electrical Characteristics (continued)**

(V<sub>DD</sub> = 2.7V to 5.5V, V<sub>DDIO</sub> = 1.8V to 5.5V, V<sub>GND</sub> = 0V, C<sub>L</sub> = 200pF, R<sub>L</sub> = 2k $\Omega$ , T<sub>A</sub> = -40°C to +125°C, unless otherwise noted.) (Note 3)

| PARAMETER              | SYMBOL           | CON                            | MIN                             | ТҮР | MAX | UNITS |    |

|------------------------|------------------|--------------------------------|---------------------------------|-----|-----|-------|----|

| SCLK Fall to DOUT Hold | t <sub>DOH</sub> | DPHA = 0, $C_{LOAD}$ =         | 2                               |     |     | ns    |    |

| SCLK Rise to DOUT Hold | t <sub>DOH</sub> | DPHA = 1, C <sub>LOAD</sub> =  | · 0pF                           | 2   |     |       | ns |

| CSB Fall to DOUT Fall  | tDOE             | Enable time, C <sub>LOAD</sub> | = 20pF                          |     |     | 20    | ns |

|                        |                  | Diachla tima                   | 2.7V < V <sub>DDIO</sub> < 5.5V |     |     | 20    |    |

| CSB Rise to DOUT Hi-Z  | <sup>t</sup> doz | Disable time                   | 1.8V < V <sub>DDIO</sub> < 2.7V |     |     | 40    | ns |

**Note 3:** Electrical specifications are production tested at  $T_A = +25^{\circ}$ C. Specifications over the entire operating temperature range are guaranteed by design and characterization. Typical specifications are at  $T_A = +25^{\circ}$ C.

**Note 4:** DC performance is tested without load,  $V_{REF} = V_{DD}$ .

Note 5: Linearity is tested with unloaded outputs to within 20mV of GND and V<sub>DD</sub>.

**Note 6:** Gain and offset calculated from measurements made with  $V_{REF} = V_{DD}$  at codes 30 and 4065 for MAX5725, codes 8 and 1016 for MAX5724, and codes 2 and 254 for MAX5723.

Note 7: Subject to zero- and full-scale error limits and V<sub>REF</sub> settings.

Note 8: Measured with all other DAC outputs at midscale with one channel transitioning 0 to full scale.

Note 9: On power-up, the device initiates an internal 200µs (typ) calibration sequence. All commands issued during this time will be ignored.

Note 10: Guaranteed by design.

Note 11: All channels active at  $V_{FS}$ , unloaded. Static logic inputs with  $V_{IL} = V_{GND}$  and  $V_{IH} = V_{DDIO}$  for all inputs.

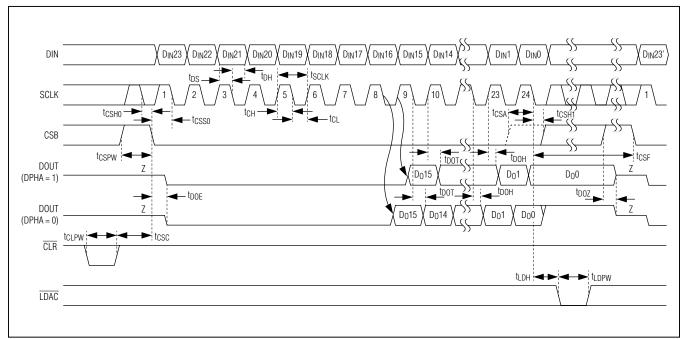

Figure 1. SPI Serial Interface Timing Diagram

# Ultra-Small, Octal-Channel, 8-/10-/12-Bit Buffered Output DACs with Internal Reference and SPI Interface

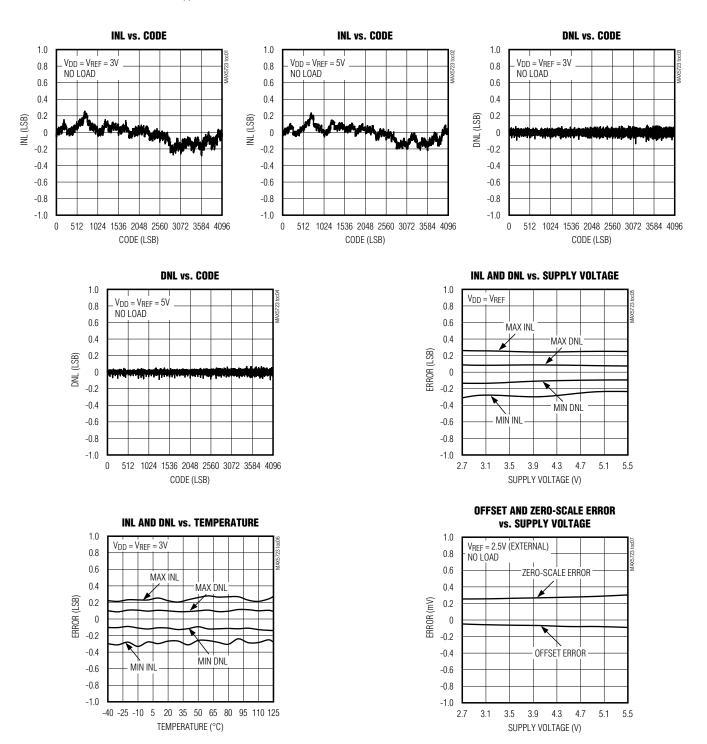

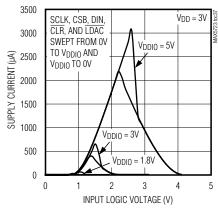

### **Typical Operating Characteristics**

(MAX5725, 12-bit performance,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

# Ultra-Small, Octal-Channel, 8-/10-/12-Bit Buffered Output DACs with Internal Reference and SPI Interface

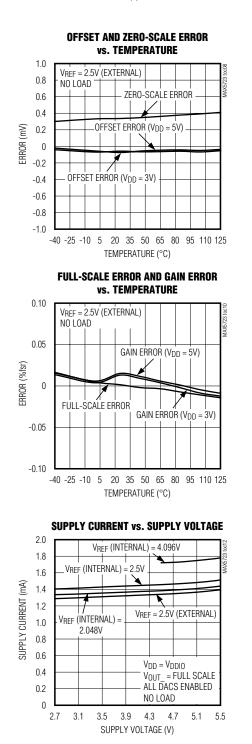

### **Typical Operating Characteristics (continued)**

(MAX5725, 12-bit performance,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

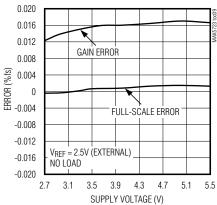

#### FULL-SCALE ERROR AND GAIN ERROR vs. Supply voltage

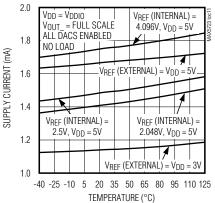

SUPPLY CURRENT vs. TEMPERATURE

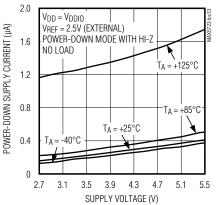

POWER-DOWN MODE SUPPLY CURRENT vs. Supply Voltage

# Ultra-Small, Octal-Channel, 8-/10-/12-Bit Buffered Output DACs with Internal Reference and SPI Interface

### **Typical Operating Characteristics (continued)**

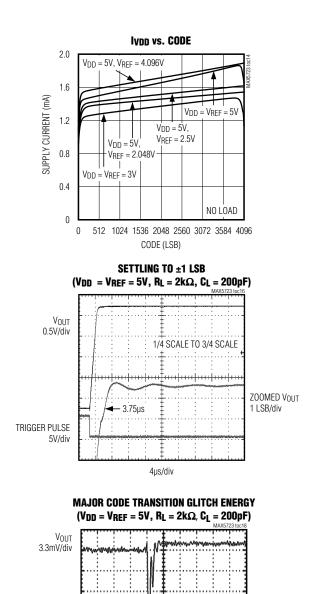

(MAX5725, 12-bit performance,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

1 LSB CHANGE (MIDCODE TRANSITION

FROM 0x7FF TO 0x800) GLITCH ENERGY = 6 7nV

TRIGGER PULSE

5V/div

# Ultra-Small, Octal-Channel, 8-/10-/12-Bit Buffered Output DACs with Internal Reference and SPI Interface

### **Typical Operating Characteristics (continued)**

(MAX5725, 12-bit performance,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

CHANNEL-TO-CHANNEL FEEDTHROUGH (VDD = VREF = 5V, TA = +25°C, NO LOAD)

4µs/div

CHANNEL-TO-CHANNEL FEEDTHROUGH (VDD = 5V, VREF = 4.096V, TA = +25°C, NO LOAD) MAXS723 toc23

CHANNEL-TO-CHANNEL FEEDTHROUGH (VDD = 5V, VREF = 4.096V (INTERNAL),  $T_A = +25^{\circ}C$ ,  $R_L = 2k\Omega$ ,  $C_L = 200pF$

# Ultra-Small, Octal-Channel, 8-/10-/12-Bit Buffered Output DACs with Internal Reference and SPI Interface

### **Typical Operating Characteristics (continued)**

(MAX5725, 12-bit performance,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

#### **OUTPUT LOAD REGULATION** 10 $V_{DD} = V_{REF}$ 8 6 $V_{DD} = 5V$ 4 ΔV0UT (mV) 2 0 V<sub>DD</sub> = 3V -2 -4 -6 -8 -10 -30 -20 -10 0 10 20 30 40 50 60 IOUT (mA)

HEADROOM AT RAILS vs. OUTPUT CURRENT (V<sub>DD</sub> = V<sub>REF</sub>)

#### NOISE-VOLTAGE DENSITY vs. FREQUENCY (DAC AT MIDSCALE)

# Ultra-Small, Octal-Channel, 8-/10-/12-Bit Buffered Output DACs with Internal Reference and SPI Interface

# **Typical Operating Characteristics (continued)**

(MAX5725, 12-bit performance,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

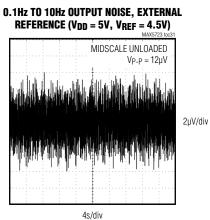

o/ulv

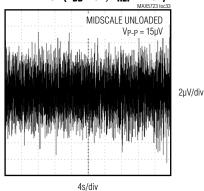

0.1Hz TO 10Hz OUTPUT NOISE, INTERNAL REFERENCE ( $V_{DD} = 5V$ ,  $V_{REF} = 2.5V$ )

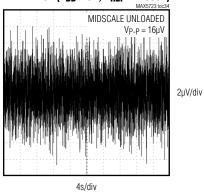

0.1Hz TO 10Hz OUTPUT NOISE, INTERNAL REFERENCE ( $V_{DD} = 5V$ ,  $V_{REF} = 2.048V$ )

2µV/div

0.1Hz TO 10Hz OUTPUT NOISE, INTERNAL REFERENCE (V<sub>DD</sub> = 5V, V<sub>REF</sub> = 4.096V)

www.maximintegrated.com

# Ultra-Small, Octal-Channel, 8-/10-/12-Bit Buffered Output DACs with Internal Reference and SPI Interface

### **Typical Operating Characteristics (continued)**

(MAX5725, 12-bit performance,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

SUPPLY CURRENT vs. SUPPLY VOLTAGE

WATCHDOG TIMER PERIOD HISTOGRAM

WATCHDOG TIMER FREQUENCY vs. temperature

# Ultra-Small, Octal-Channel, 8-/10-/12-Bit Buffered Output DACs with Internal Reference and SPI Interface

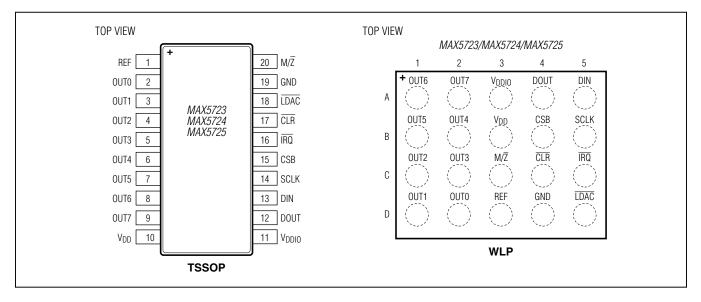

# **Pin Configurations**

### **Pin Description**

|       | PIN |                   | FUNCTION                                                                                                                          |

|-------|-----|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| TSSOP | WLP | NAME              | FUNCTION                                                                                                                          |

| 1     | D3  | REF               | Reference Voltage Input/Output                                                                                                    |

| 2     | D2  | DAC0              | DAC Channel 0 Voltage Output                                                                                                      |

| 3     | D1  | OUT1              | DAC Channel 1 Voltage Output                                                                                                      |

| 4     | C1  | OUT2              | DAC Channel 2 Voltage Output                                                                                                      |

| 5     | C2  | OUT3              | DAC Channel 3 Voltage Output                                                                                                      |

| 6     | B2  | OUT4              | DAC Channel 4 Voltage Output                                                                                                      |

| 7     | B1  | OUT5              | DAC Channel 5 Voltage Output                                                                                                      |

| 8     | A1  | OUT6              | DAC Channel 6 Voltage Output                                                                                                      |

| 9     | A2  | OUT7              | DAC Channel 7 Voltage Output                                                                                                      |

| 10    | B3  | V <sub>DD</sub>   | Analog Supply Voltage                                                                                                             |

| 11    | A3  | V <sub>DDIO</sub> | Digital Supply Voltage                                                                                                            |

| 12    | A4  | DOUT              | SPI Serial Data Output                                                                                                            |

| 13    | A5  | DIN               | SPI Serial Data Input                                                                                                             |

| 14    | B5  | SCLK              | SPI Serial Clock Input                                                                                                            |

| 15    | B4  | CSB               | SPI Chip-Select Input                                                                                                             |

| 16    | C5  | ĪRQ               | Active-Low Open Drain Interrupt Output. IRQ low indicates watchdog timeout.                                                       |

| 17    | C4  | CLR               | Active-Low Asynchronous DAC Clear Input                                                                                           |

| 18    | D5  | LDAC              | Active-Low Asynchronous DAC Load Input                                                                                            |

| 19    | D4  | GND               | Ground                                                                                                                            |

| 20    | C3  | M/Z               | DAC Output Reset Selection. Connect $M/\overline{Z}$ to GND for zero-scale and connect $M/\overline{Z}$ to $V_{DD}$ for midscale. |

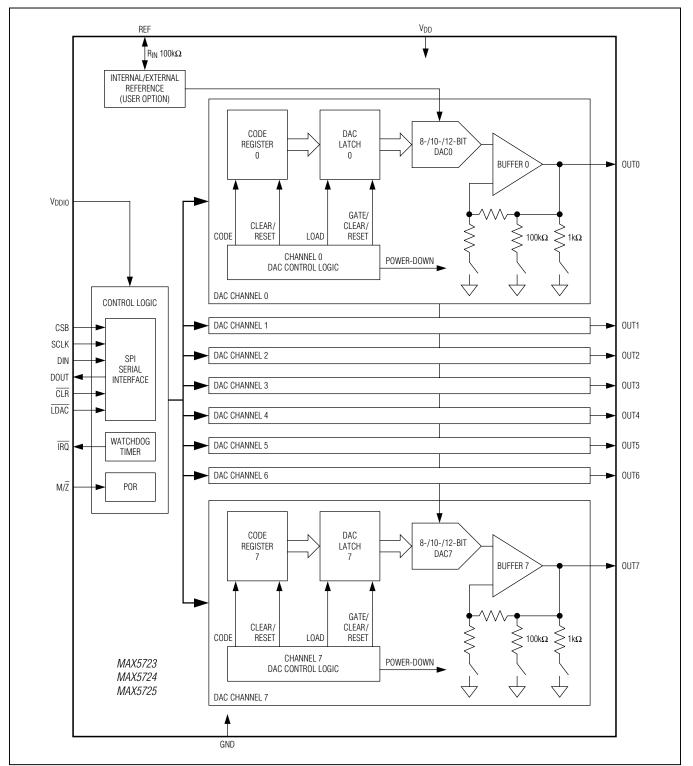

### **Detailed Description**

The MAX5723/MAX5724/MAX5725 are 8-channel, lowpower, 8-/10-/12-bit buffered voltage-output DACs. The 2.7V to 5.5V wide supply voltage range and low-power consumption accommodates most low-power and lowvoltage applications. The devices present a  $100k\Omega$  load to the external reference. The internal output buffers allow rail-to-rail operation. An internal voltage reference is available with software-selectable options of 2.048V, 2.500V, or 4.096V. The devices feature a fast 4-wire SPI/QSPI/MICROWIRE/DSP-compatible serial interface to save board space and reduce the complexity in isolated applications interface. The MAX5723/MAX5724/ MAX5725 include a serial-in/parallel-out shift register, internal CODE and DAC registers, a power-on-reset (POR) circuit to initialize the DAC outputs to zero scale  $(M/\overline{Z} = 0)$  or midscale  $(M/\overline{Z} = 1)$ , and control logic.

CLR is available to asynchronously clear the DAC outputs to a user-programmable default value, independent of the serial interface. LDAC is available to simultaneously update selected DACs on one or more devices. The MAX5723/MAX5724/MAX5725 also feature user-configurable interface watchdog, with status indicated by the IRQ output.

### DAC Outputs (OUT\_)

The MAX5723/MAX5724/MAX5725 include internal buffers on all DAC outputs, which provide improved load regulation for the DAC outputs. The output buffers slew at 1V/µs (typ) and drive resistive loads are as low as 2k $\Omega$  in parallel with as much as 500pF of capacitance. The analog supply voltage (V<sub>DD</sub>) determines the maximum output voltage range of the devices since it powers the output buffers. Under no-load conditions, the output buffers drive from GND to V<sub>DD</sub>, subject to offset and gain errors. With a 2k $\Omega$  load to GND, the output buffers drive from GND to vithin 200mV of V<sub>DD</sub>. With a 2k $\Omega$  load to V<sub>DD</sub>, the output buffers drive from V<sub>DD</sub> to within 200mV of GND.

The DAC ideal output voltage is defined by:

$$V_{OUT} = V_{REF} \times \frac{D}{2^N}$$

where D = code loaded into the DAC register,  $V_{REF}$  = reference voltage, N = resolution.

# Ultra-Small, Octal-Channel, 8-/10-/12-Bit Buffered Output DACs with Internal Reference and SPI Interface

#### **Internal Register Structure**

The user interface is separated from the DAC logic to minimize digital feedthrough. Within the serial interface is an input shift register, the contents of which can be routed to control registers, individual, or multiple DACs as determined by the user command.

Within each DAC channel there is a CODE register followed by a DAC latch register (see the <u>Detailed</u> <u>Functional Diagram</u>). The contents of the CODE register hold pending DAC output settings which can later be loaded into the DAC registers. The CODE register can be updated using both CODE and CODE\_LOAD user commands. The contents of the DAC register hold the current DAC output settings. The DAC register can be updated directly from the serial interface using the CODE\_LOAD commands or can upload the current contents of the CODE register using LOAD commands or the LDAC logic input.

The contents of both CODE and DAC registers are maintained during power-down states, so that when the DACs are powered on, they return to their previously stored output settings. Any CODE or LOAD commands issued during power-down states continue to update the register contents.

Once the device is powered up, each DAC channel can be independently programmed with a desired RETURN value using the RETURN command. This becomes the value the CODE and DAC registers will use in the event of any watchdog, clear or gate activity, as selected by the DEFAULT command.

Hardware CLR operations and SW\_CLEAR commands return the contents of all CODE and DAC registers to their user-selected defaults. SW\_RESET commands will reset CODE and DAC register contents to their M/Z selected initial codes. A SW\_GATE state can be used to momentarily hold selected DAC outputs in their DEFAULT positions. The contents of CODE and DAC registers can be manipulated by watchdog timer activity, enabling a variety of safety features.

#### Internal Reference

The MAX5723/MAX5724/MAX5725 include an internal precision voltage reference that is software selectable to be 2.048V, 2.500V, or 4.096V. When an internal reference is selected, that voltage is available on the REF output for other external circuitry (see the <u>Typical Operating</u> *Circuits*) and can drive loads down to  $25k\Omega$ .

### **External Reference**

The external reference input has a typical input impedance of 100k $\Omega$  and accepts an input voltage from +1.24V to V<sub>DD</sub>. Apply an external voltage between REF and GND to use an external reference. The MAX5723/MAX5724/MAX5725 power up and reset to external reference mode. Visit **www.maximintegrated.com/products/references** for a list of available external voltage-reference devices.

### M/Z Input

The MAX5723/MAX5724/MAX5725 feature a pin-selectable DAC reset state using the M/Z input. Upon a poweron reset, all CODE and DAC data registers are reset to zero scale (M/Z = GND) or midscale (M/Z = V<sub>DD</sub>). M/Z is referenced to V<sub>DD</sub> (not V<sub>DDIO</sub>). In addition, M/Z must be valid at the time the device is powered up—connect M/Z directly to V<sub>DD</sub> or GND.

### Load DAC (LDAC) Input

The MAX5723/MAX5724/MAX5725 feature an active-low asynchronous  $\overline{\text{LDAC}}$  logic input that allows DAC outputs to update simultaneously. Connect  $\overline{\text{LDAC}}$  to V<sub>DDIO</sub> or keep  $\overline{\text{LDAC}}$  high during normal operation when the device is controlled only through the serial interface. Drive  $\overline{\text{LDAC}}$  low to update the DAC outputs with data from the CODE registers. Holding  $\overline{\text{LDAC}}$  low causes the DAC registers to become transparent and CODE data is passed through to the DAC registers immediately updating the DAC outputs. A software CONFIG command can be used to configure the  $\overline{\text{LDAC}}$  operation of each DAC independently.

### Clear (CLR) Input

The MAX5723/MAX5724/MAX5725 feature an asynchronous active-low  $\overline{\text{CLR}}$  logic input that simultaneously sets all selected DAC outputs to their programmable DEFAULT states. Driving  $\overline{\text{CLR}}$  low clears the contents of both the CODE and DAC registers and also ignores any on-going SPI command which modifies registers associated with a DAC configured to accept clear operations. To allow a new SPI command, drive  $\overline{\text{CLR}}$  high, satisfying the t<sub>CSC</sub> timing requirement. A software CONFIG com-

# Ultra-Small, Octal-Channel, 8-/10-/12-Bit Buffered Output DACs with Internal Reference and SPI Interface

mand can be used to configure the clear operation of each DAC independently.

#### Watchdog Feature

The MAX5723/MAX5724/MAX5725 feature an interface watchdog timer with programmable timeout duration. This monitors the I/O interface for activity and integrity. If the watchdog is enabled, the host processor must write a valid command to the device within the timeout period to prevent a timeout. If the watchdog is allowed to timeout, selected DAC outputs are returned to the programmable DEFAULT state, protecting the system against control faults.

By default, all watchdog features are disabled; users wishing to activate any watchdog feature must configure the device accordingly. Individual DAC channels can be configured using the CONFIG command to accept the watchdog alarm and to gate, clear, or hold their outputs in response to an alarm. A watchdog refresh event and watchdog behavior upon timeout is defined by a programmable safety level using the WDOG\_CONFIG command.

### **IRQ** Output

The MAX5723/MAX5724/MAX5725 feature an active-low open-drain interrupt output indicating to the host when a watchdog timeout has occurred.

### Interface Power Supply (V<sub>DDIO</sub>)

The MAX5723/MAX5724/MAX5725 feature a separate supply input ( $V_{DDIO}$ ) for the digital interface (1.8V to 5.5V). Connect  $V_{DDIO}$  to the I/O supply of the host processor.

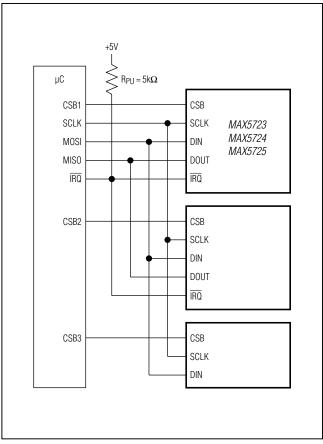

### **SPI Serial Interface**

The MAX5723/MAX5724/MAX5725 4-wire serial interface is compatible with MICROWIRE, SPI, QSPI, and DSPs. The interface provides three inputs, SCLK, CSB, and DIN. The chip-select input (CSB, active-low) frames the data loaded through the serial data input (DIN). Following a CSB input high-to-low transition, the data is shifted in synchronously and latched into the input register on each falling edge of the serial clock input (SCLK). Each serial operation word is 24-bits long. The DAC data is left justified as shown in Table 1. The serial

| PART    | B15 | B14 | B13 | B12 | B11 | B10 | B9 | B8 | B7 | B6 | B5 | B4 | B3 | B2 | B1 | B0 |

|---------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| MAX5723 | D7  | D6  | D5  | D4  | D3  | D2  | D1 | D0 | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  |

| MAX5724 | D9  | D8  | D7  | D6  | D5  | D4  | D3 | D2 | D1 | D0 | Х  | Х  | Х  | Х  | Х  | Х  |

| MAX5725 | D11 | D10 | D9  | D8  | D7  | D6  | D5 | D4 | D3 | D2 | D1 | D0 | Х  | Х  | Х  | Х  |

### **Table 1. Format DAC Data Bit Positions**

input register transfers its contents to the destination registers after loading 24 bits of data on the 24th SCLK falling edge. To initiate a new SPI operation, drive CSB high and then low to begin the next operation sequence, being sure to meet all relevant timing requirements. During CSB high periods, SCLK is ignored, allowing communication to other devices on the same bus. SPI operations consisting of more than 24 SCLK cycles are executed on the 24th SCLK falling edge, using the first three bytes of data available. SPI operations consisting of less than 24 SCLK cycles will not be executed. The content of the SPI operation consists of a command byte followed by a two-byte data word.

The DOUT phase for all SPI\_READ commands is determined by the readback command used, allowing the selection of the SCLK DOUT update edge best suited to the digital I/O implementation, maximizing data transfer speed and/or timing margin.

Guaranteed non-zero DOUT hold times allow the microprocessor to strobe DOUT on the same edge as the MAX5723/MAX5724/MAX5725 updates for fastest SPI read mode transfers. For example, if DPHA = 0 is used, the MAX5723/MAX5724/MAX5725 update DOUT in response to SCLK falling edges 8-23, while a microprocessor ( $\mu$ P) with low data hold time requirements can strobe in the DOUT data on SCLK falling edges 9-24. The device supports readback speeds of up to 25MHz for a microprocessor with 5ns data input setup requirements and allowing 35ns for t<sub>DOT</sub> at V<sub>DDIO</sub> > 2.7V.

Variable DOUT phase also supports microprocessors with longer data input hold time requirements. For example, if DPHA = 1 is used, the MAX5723/MAX5724/ MAX5725 updates DOUT in response to SCLK rising edges 9-24 while the microprocessor can strobe in the DOUT data on SCLK falling edges 9-24. The device supports readback speeds up to 12.5MHz for a  $\mu$ P with 5ns data input setup requirements and allowing 35ns for t<sub>DOT</sub> (assuming 50% duty cycle SCLK).

For improved readback speed while monitoring device status, the SPI\_READ\_STATUS command repeats the device status information for multiple bits, allowing polling of the device at maximum interface speeds (up to 50MHz when the readback strobe is placed away from DOUT transition edges). This transfer speed cannot be achieved for other forms of readback using the SPI\_READ\_DATA command, where more DOUT bus transitions occur.

# Ultra-Small, Octal-Channel, 8-/10-/12-Bit Buffered Output DACs with Internal Reference and SPI Interface

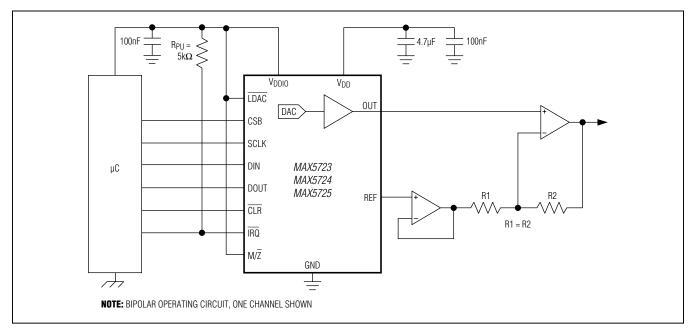

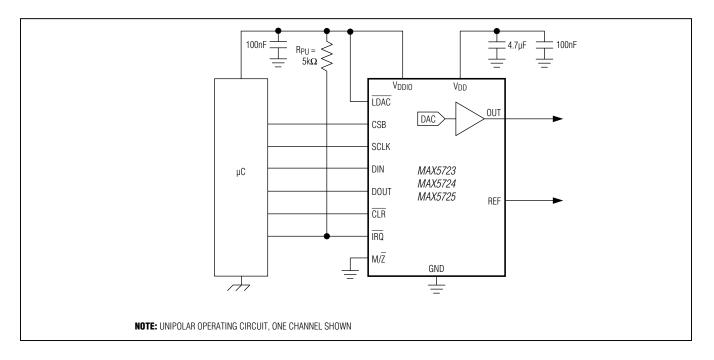

Figure 2. Typical SPI Application Circuit

Figure 1 shows the timing diagram for the complete 4-wire serial interface transmission. The DAC code settings (D) for the MAX5723/MAX5724/MAX5725 are accepted in an offset binary format (see <u>Table 1</u>). Otherwise, the expected data format for each command is listed in <u>Table 2</u>. See Figure 2 for an example of a typical SPI circuit application.

#### **SPI User-Command Register Map**

This section lists the user-accessible commands and registers for the MAX5723/MAX5724/MAX5725.

Table 2 provides detailed information about the Command Registers.

# Ultra-Small, Octal-Channel, 8-/10-/12-Bit Buffered Output DACs with Internal Reference and SPI Interface

| DESCRIPTION |                                     | Updates watchdog<br>settings and safety levels               | Sets the reference<br>operating mode. REF<br>Power (B18):<br>0 = Internal reference is<br>only powered if at least one<br>DAC is powered<br>1 = Internal reference is<br>always powered | Removes any existing<br>GATE condition | Initiates a GATE condition | Refreshes the watchdog timer | Reset the watchdog time<br>out alarm status and<br>refreshes the watchdog<br>timer | Executes a software<br>clear (all CODE and DAC<br>registers cleared to their<br>DEFAULT values) | Executes a software reset<br>(all CODE, DAC, and<br>control registers returned<br>to their power-on reset<br>values) | Configures selected DAC<br>Watchdog, GATE, LOAD,<br>and CLEAR operations.<br>DACs selected with a<br>1 in the corresponding<br>DACn bit are updated,<br>DACs with a 0 in the<br>corresponding DACn bit<br>are not impacted) |

|-------------|-------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------|------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8           |                                     | ×                                                            | ×                                                                                                                                                                                       | 0                                      | 0                          | 0                            | 0                                                                                  | 0                                                                                               | 0                                                                                                                    | ×                                                                                                                                                                                                                           |

| 臣           |                                     | Safety<br>Level<br>00: Low<br>01: Med<br>10: High<br>11: Max | ×                                                                                                                                                                                       | 0                                      | 0                          | 0                            | 0                                                                                  | 0                                                                                               | 0                                                                                                                    | ×                                                                                                                                                                                                                           |

| B2          |                                     | Sat<br>Le<br>00:<br>01:<br>10:11                             | ×                                                                                                                                                                                       | 0                                      | 0                          | 0                            | 0                                                                                  | 0                                                                                               | 0                                                                                                                    | ×                                                                                                                                                                                                                           |

| B3          |                                     | WD_MASK                                                      | ×                                                                                                                                                                                       | 0                                      | 0                          | 0                            | 0                                                                                  | 0                                                                                               | 0                                                                                                                    | CLEAR_ENB                                                                                                                                                                                                                   |

| B4          |                                     | [0;                                                          | ×                                                                                                                                                                                       | -                                      | -                          | -                            | -                                                                                  | -                                                                                               | -                                                                                                                    | LDAC_ENB                                                                                                                                                                                                                    |

| B5          |                                     | TIMEOUT<br>SELECTION[3:0]                                    | ×                                                                                                                                                                                       | -                                      | -                          | -                            | -                                                                                  | -                                                                                               | -                                                                                                                    | GATE_ENB                                                                                                                                                                                                                    |

| B6          |                                     | TIME                                                         | ×                                                                                                                                                                                       | 0                                      | 0                          | 0                            | 0                                                                                  | 0                                                                                               | 0                                                                                                                    | WDOG<br>Config.<br>00: DIS<br>01: GATE<br>10: CLR<br>11: HOLD                                                                                                                                                               |

| B7          |                                     | SE                                                           | ×                                                                                                                                                                                       | 0                                      | 0                          | 0                            | 0                                                                                  | 0                                                                                               | 0                                                                                                                    | WE<br>Co<br>01: (0<br>11: H                                                                                                                                                                                                 |

| B8          |                                     |                                                              | ×                                                                                                                                                                                       | 0                                      | 0                          | 0                            | 0                                                                                  | 0                                                                                               | 0                                                                                                                    | DAC0                                                                                                                                                                                                                        |

| B9          |                                     | [4]                                                          | ×                                                                                                                                                                                       | -                                      | -                          | -                            | -                                                                                  | -                                                                                               |                                                                                                                      | DAC1                                                                                                                                                                                                                        |

| B10         |                                     | TIMEOUT SELECTION[11:4]                                      | ×                                                                                                                                                                                       | -                                      | -                          | -                            | -                                                                                  | -                                                                                               |                                                                                                                      | DAC2                                                                                                                                                                                                                        |

| B11         |                                     | ECTIO                                                        | ×                                                                                                                                                                                       | 0                                      | 0                          | 0                            | 0                                                                                  | 0                                                                                               | 0                                                                                                                    | DAC3                                                                                                                                                                                                                        |

| B12         |                                     | JT SEL                                                       | ×                                                                                                                                                                                       | -                                      | -                          | -                            | -                                                                                  | -                                                                                               | <del></del>                                                                                                          | DAC4                                                                                                                                                                                                                        |

| B13         |                                     | MEOL                                                         | ×                                                                                                                                                                                       | 0                                      | 0                          | 0                            | 0                                                                                  | 0                                                                                               | 0                                                                                                                    | DAC5                                                                                                                                                                                                                        |