### Data Sheet February 1997

# microelectronics group

# **ATT3000 Series Field-Programmable Gate Arrays**

#### Features

- High performance:

- Up to 270 MHz toggle rates

- 4-input LUT delays <2.7 ns

- User-programmable gate arrays

- Unlimited reprogrammability

- Easy design iteration through in-system logic changes

- Flexible array architecture:

- Compatible arrays ranging from 1500 to 6000 gate logic complexity

- Extensive register, combinatorial, and I/O capabilities

- Low-skew clock nets

- High fan-out signal distribution

- Internal 3-state bus capabilities

- TTL or CMOS input thresholds

- On-chip oscillator amplifier

- Standard product availability:

- Low-power 0.55 µm CMOS, static memory technology

- Pin-for-pin compatible with Xilinx\* XC3000\* and XC3100\* families

- Cost-effective for volume production

- 100% factory pretested

- Selectable configuration modes

- ORCA<sup>TM</sup> Foundry for ATT3000 Development System support

- All FPGAs processed on a QML-certified line

- Extensive packaging options

## Description

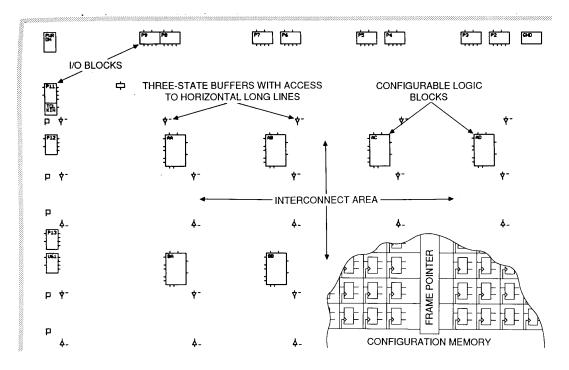

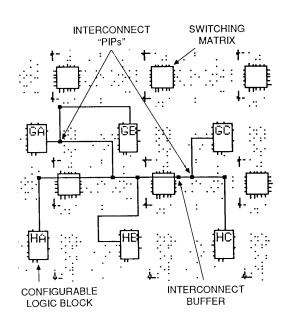

The CMOS ATT3000 Series Field-Programmable Gate Array (FPGA) family provides a group of highdensity, digital integrated circuits. Their regular, extendable, flexible, user-programmable array architecture is composed of a configuration program store plus three types of configurable elements: a perimeter of I/O blocks, a core array of logic blocks, and resources for interconnection. The general structure of an FPGA is shown in Figure 1.

The ORCA Foundry for ATT3000 Development System provides automatic place and route of netlists. Logic and timing simulation are available as design verification alternatives. The design editor is used for interactive design optimization and to compile the data pattern that represents the configuration program.

The FPGA's user-logic functions and interconnections are determined by the configuration program data stored in internal static memory cells. The program can be loaded in any of several modes to accommodate various system requirements. The program data resides externally in an EEPROM, EPROM, or ROM on the application circuit board, or on a floppy disk or hard disk. On-chip initialization logic provides for optional automatic loading of program data at powerup. A serial configuration PROM can provide a very simple serial configuration program storage.

*Xilinx*, *XC3000*, and *XC3100* are registered trademarks of Xilinx, Inc.

| FPGA    | Max<br>Logic<br>Gates | Typical Gate<br>Range | Configurable<br>Logic<br>Blocks | Array   | User I/Os<br>Max | Flip-<br>Flops | Horizontal<br>Long Lines | Configuration<br>Data Bits |

|---------|-----------------------|-----------------------|---------------------------------|---------|------------------|----------------|--------------------------|----------------------------|

| ATT3020 | 1,500                 | 1,000—1,500           | 64                              | 8 x 8   | 64               | 256            | 16                       | 14,779                     |

| ATT3030 | 2,000                 | 1,500—2,000           | 100                             | 10 x 10 | 80               | 360            | 20                       | 22,176                     |

| ATT3042 | 3,000                 | 2,000—3,000           | 144                             | 12 x 12 | 96               | 480            | 24                       | 30,784                     |

| ATT3064 | 4,500                 | 3,500—4,500           | 224                             | 16 x 14 | 120              | 688            | 32                       | 46,064                     |

| ATT3090 | 6,000                 | 5,000—6,000           | 320                             | 20 x 16 | 144              | 928            | 40                       | 64,160                     |

#### Table 1. ATT3000 Series FPGAs

Page

# **Table of Contents**

Contents

| Contents                        | Page |

|---------------------------------|------|

| Features                        | 1    |

| Description                     | 1    |

| Architecture                    | 3    |

| Configuration Memory            | 4    |

| I/O Block                       |      |

| Summary of I/O Options          |      |

| Configurable Logic Block        |      |

| Programmable Interconnect       |      |

| General-Purpose Interconnect    |      |

| Direct Interconnect             |      |

| Long Lines                      | 13   |

| Internal Buses                  |      |

| Crystal Oscillator              |      |

| Configuration                   |      |

| Initialization Phase            |      |

| Configuration Data              |      |

| Configuration Modes             |      |

| Master Mode                     |      |

| Peripheral Mode                 |      |

| Slave Mode                      |      |

| Daisy Chain                     | 26   |

| Special Configuration Functions |      |

| Input Thresholds                |      |

| Readback                        |      |

| Reprogram                       |      |

| DONE Pull-Up                    |      |

| DONE Timing                     |      |

| RESET Timing                    |      |

| Crystal Oscillator Division     | 28   |

| Performance                     | 29 |

|---------------------------------|----|

| Device Performance              | 29 |

| Logic Block Performance         | 30 |

| Interconnect Performance        |    |

| Power                           | 32 |

| Power Distribution              | 32 |

| Power Dissipation               |    |

| Pin Information                 |    |

| Pin Assignments                 | 39 |

| Package Thermal Characteristics |    |

| Package Coplanarity             | 51 |

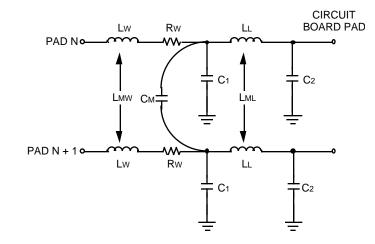

| Package Parasitics              |    |

| Absolute Maximum Ratings        | 53 |

| Electrical Characteristics      |    |

| Outline Diagrams                | 68 |

| Terms and Definitions           | 68 |

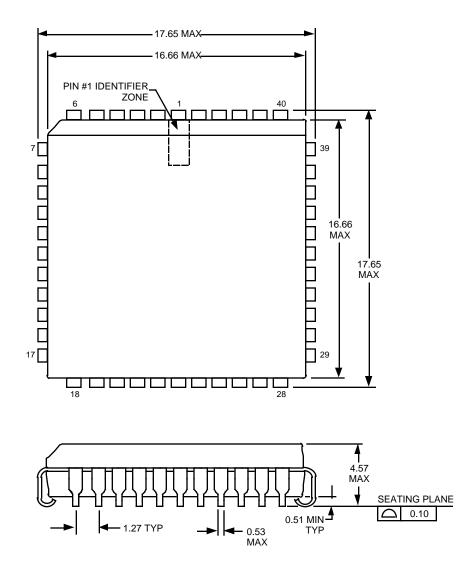

| 44-Pin PLCC                     |    |

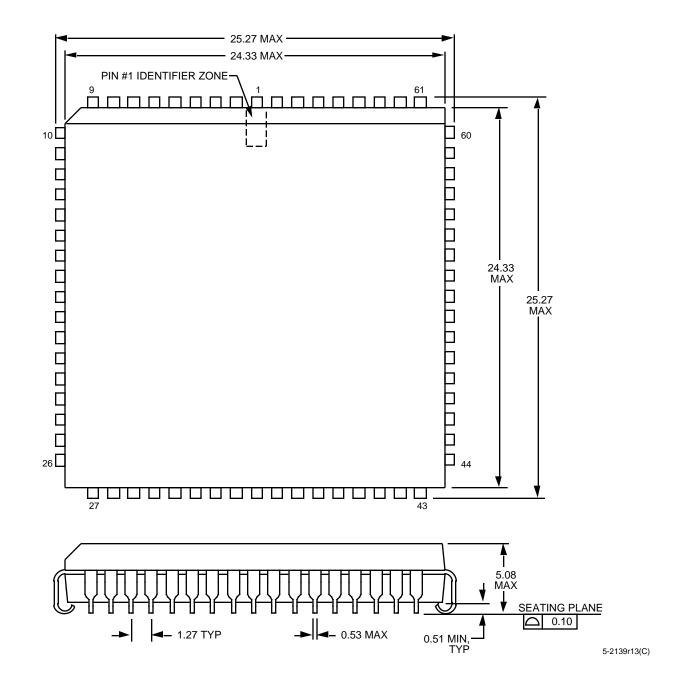

| 68-Pin PLCC                     | 69 |

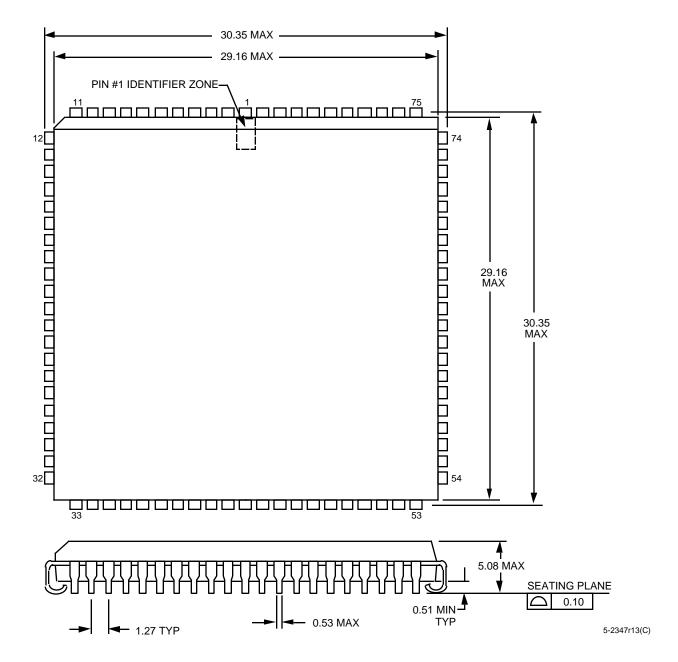

| 84-Pin PLCC                     | 70 |

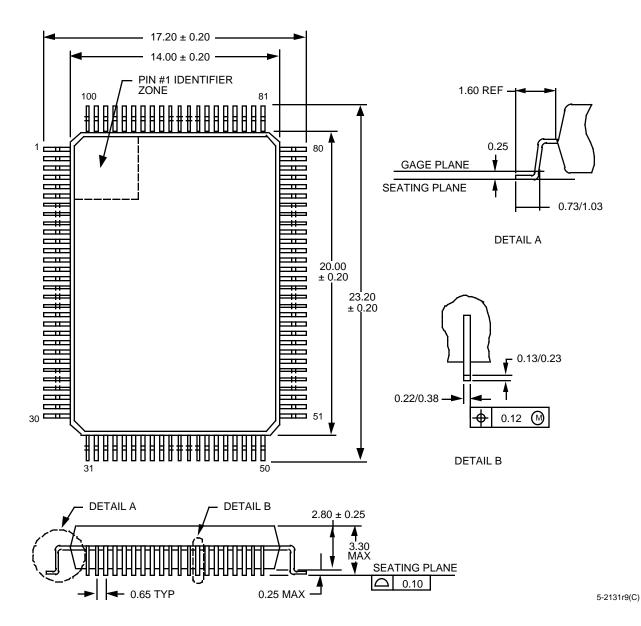

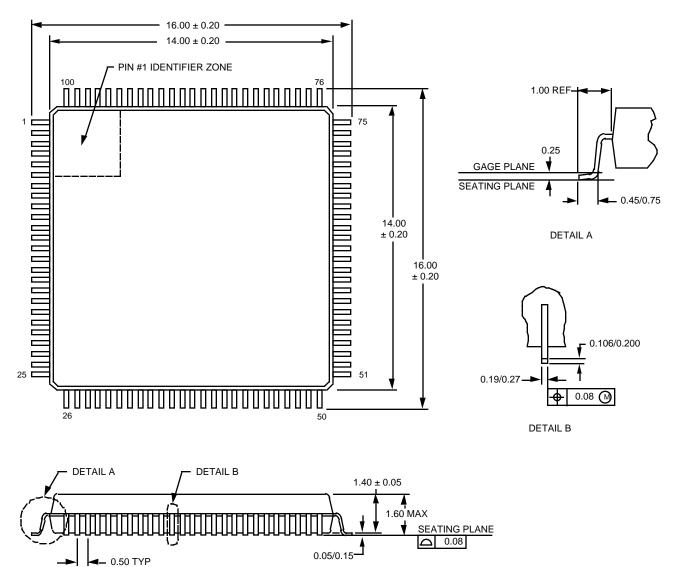

| 100-Pin QFP                     | 71 |

| 100-Pin TQFP                    | 72 |

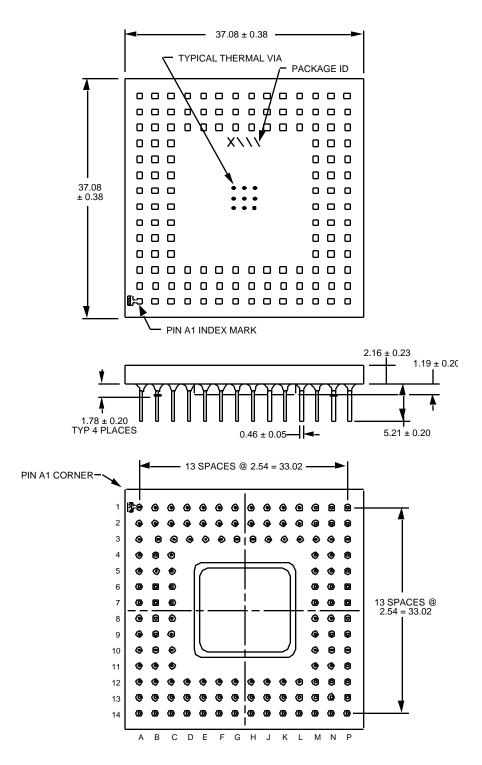

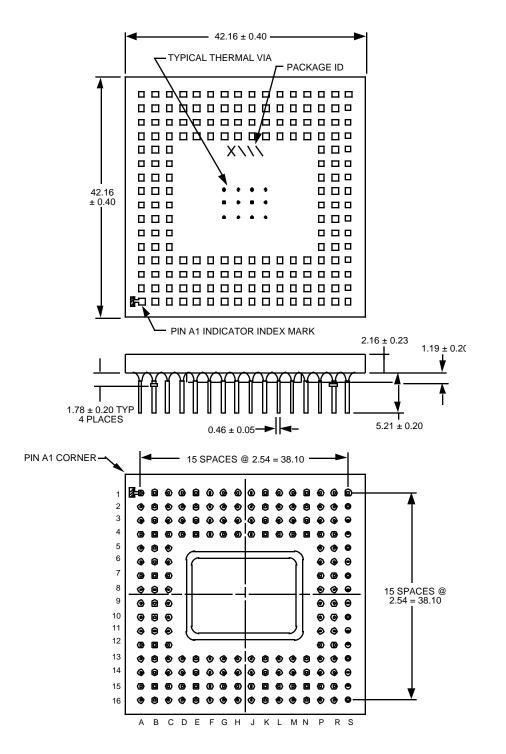

| 132-Pin PPGA                    |    |

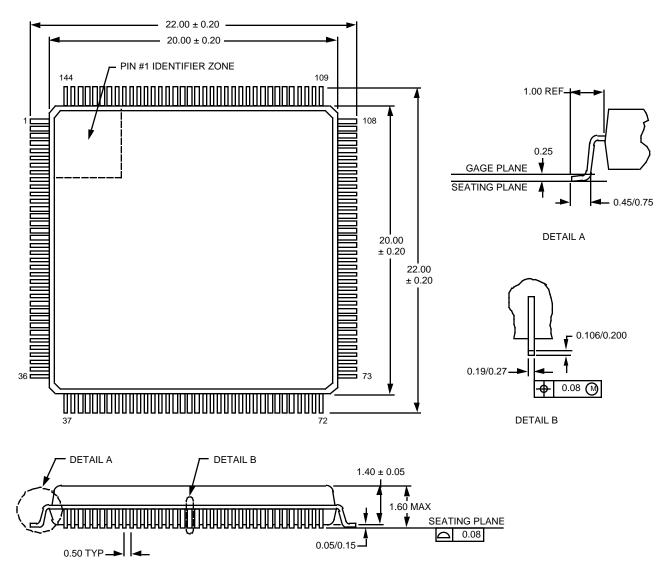

| 144-Pin TQFP                    | 74 |

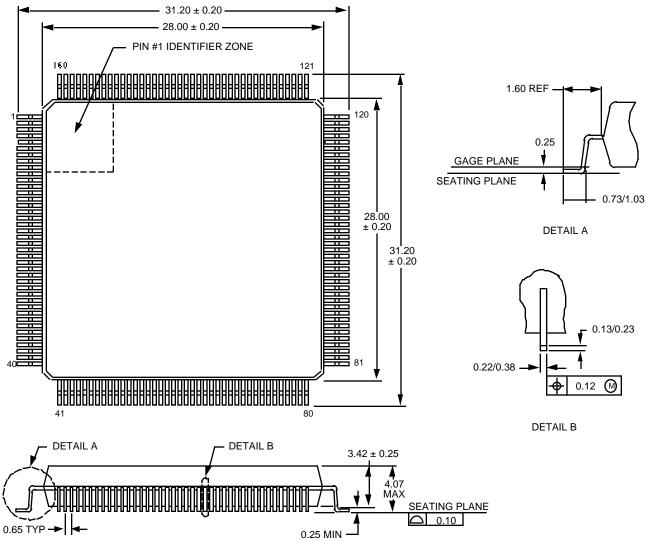

| 160-Pin QFP                     | 75 |

| 175-Pin PPGA                    | 76 |

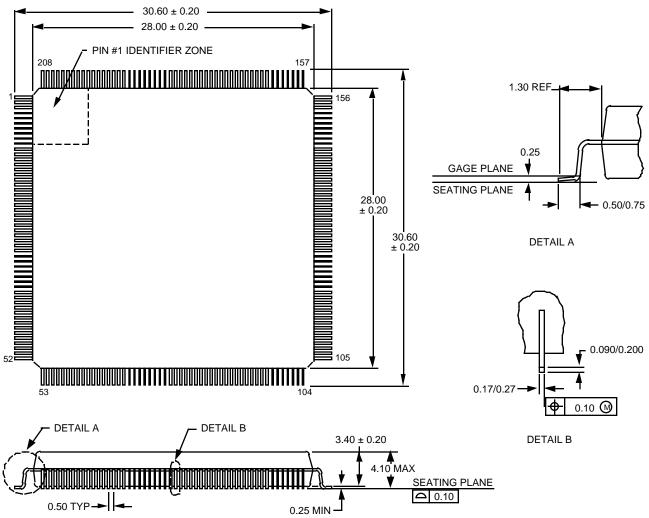

| 208-Pin SQFP                    | 77 |

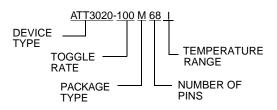

| Ordering Information            | 78 |

|                                 |    |

## Architecture

The perimeter of configurable I/O blocks (IOBs) provides a programmable interface between the internal logic array and the device package pins. The array of configurable logic blocks (CLBs) performs userspecified logic functions. The interconnect resources are programmed to form networks, carrying logic signals among blocks, analogous to printed-circuit board traces connecting MSI/SSI packages.

The blocks' logic functions are implemented by programmed look-up tables. Functional options are implemented by program-controlled multiplexers. Interconnecting networks between blocks are implemented with metal segments joined by programcontrolled pass transistors. These functions of the FPGA are established by a configuration program which is loaded into an internal, distributed array of configuration memory cells. The configuration program is loaded into the FPGA at powerup and may be reloaded on command. The FPGA includes logic and control signals to implement automatic or passive configuration. Program data may be either bit serial or byte parallel. The *ORCA* Foundry for ATT3000 Development System generates the configuration program bit stream used to configure the FPGA. The memory loading process is independent of the user logic functions.

Figure 1. Field-Programmable Gate Array Structure

## **Configuration Memory**

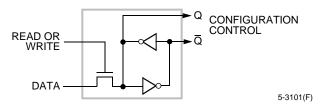

The static memory cell used for the configuration memory in the FPGA has been designed specifically for high reliability and noise immunity. Integrity of the FPGA configuration memory based on this design is ensured even under various adverse conditions. Compared with other programming alternatives, static memory is believed to provide the best combination of high density, high performance, high reliability, and comprehensive testability.

As shown in Figure 2, the basic memory cell consists of two CMOS inverters plus a pass transistor used for writing and reading cell data. The cell is only written to during configuration and only read from during readback. During normal operation, the cell provides continuous control and the pass transistor is off and does not affect cell stability. This is quite different from the operation of conventional memory devices, in which the cells are frequently read and rewritten. The memory cell outputs Q and  $\overline{Q}$  use full ground and Vcc levels and provide continuous, direct control. The additional capacitive load and the absence of address decoding and sense amplifiers provide high stability to the cell. Due to their structure, the configuration memory cells are not affected by extreme power supply excursions or very high levels of alpha particle radiation. Soft errors have not been observed in reliability testing.

Two methods of loading configuration data use serial data, while three use byte-wide data. The internal configuration logic utilizes framing information, embedded in the program data by the *ORCA* Foundry Development System, to direct memory cell loading. The serial data framing and length count preamble provide programming compatibility for mixes of various Lucent programmable gate arrays in a synchronous, serial, daisy-chain fashion.

Figure 2. Static Configuration Memory Cell

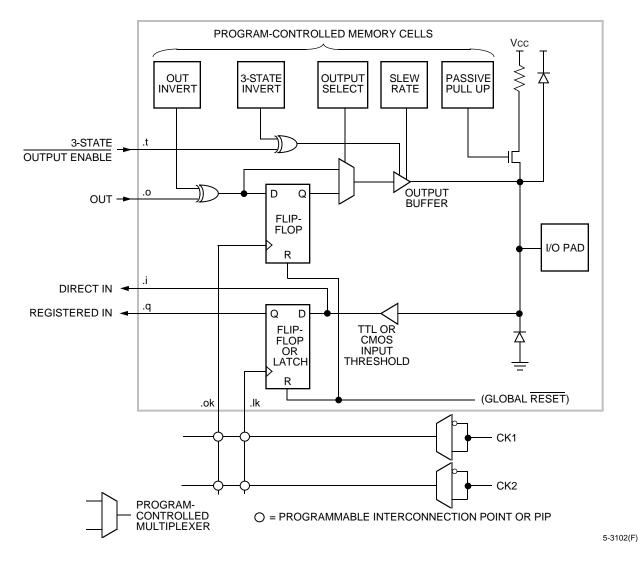

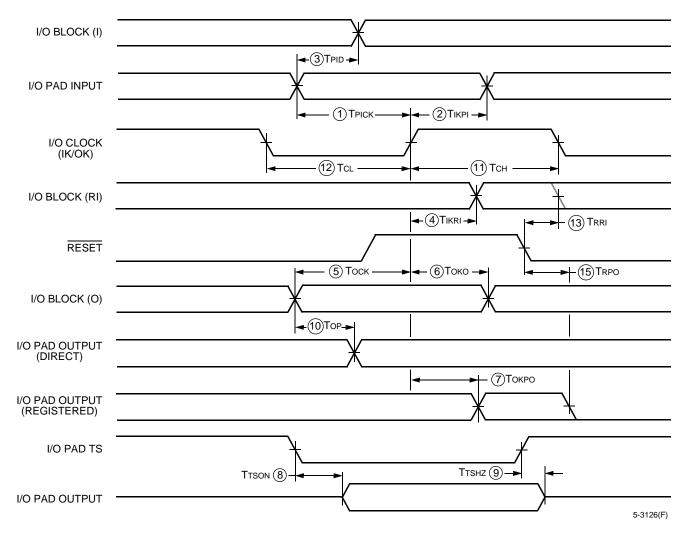

## I/O Block

Each user-configurable I/O block (IOB), shown in Figure 3, provides an interface between the external package pin of the device and the internal user logic. Each IOB includes both registered and direct input paths and a programmable 3-state output buffer which may be driven by a registered or direct output signal. Configuration options allow each IOB an inversion, a controlled slew rate, and a high-impedance pull-up. Each input circuit also provides input clamping diodes to provide electrostatic protection and circuits to inhibit latch-up produced by input currents.

The input buffer portion of each IOB provides threshold detection to translate external signals applied to the

package pin to internal logic levels. The global inputbuffer threshold of the IOB can be programmed to be compatible with either TTL or CMOS levels. The buffered input signal drives the data input of a storage element which may be configured as a positive-edge triggered D flip-flop or a low-level transparent latch. The sense of the clock can be inverted (negative edge/high transparent) as long as all IOBs on the same clock net use the same clock sense. Clock/load signals (IOB pins .ik and .ok) can be selected from either of two die edge metal lines. I/O storage elements are reset during configuration or by the active-low chip RESET input. Both direct input (from IOB pin .i) and registered input (from IOB pin .q) signals are available for interconnect.

Figure 3. Input/Output Block

## I/O Block (continued)

For reliable operation, inputs should have transition times of less than 100 ns and should not be left floating. Floating CMOS input-pin circuits might be at threshold and produce oscillations. This can produce additional power dissipation and system noise. A typical hysteresis of about 300 mV reduces sensitivity to input noise. Each user IOB includes a programmable high-impedance pull-up resistor which is selected by the program to provide a constant high for otherwise undriven package pins. Normal CMOS handling precautions should be observed.

Flip-flop loop delays for the IOB and logic block flipflops are approximately 3 ns. This short delay provides good performance under asynchronous clock and data conditions. Short loop delays minimize the probability of a metastable condition which can result from assertion of the clock during data transitions. Because of the short loop delay characteristic in the FPGA, the IOB flip-flops can be used to synchronize external signals applied to the device. When synchronized in the IOB, the signals can be used internally without further consideration of their clock relative timing, except as it applies to the internal logic and routing path delays.

Output buffers of the IOBs provide CMOS-compatible 4 mA source-or-sink drive for high fan-out CMOS or TTL compatible signal levels. The network driving IOB pin .o becomes the registered or direct data source for the output buffer. The 3-state control signal (IOB pin .t) can control output activity. An open-drain type output may be obtained by using the same signal for driving the output and 3-state signal nets so that the buffer output is enabled only for a LOW.

Configuration program bits for each IOB control features such as optional output register, logical signal inversion, and 3-state and slew rate control of the output.

The program-controlled memory cells in Figure 3 control the following options:

- Logical inversion of the output is controlled by one configuration program bit per IOB.

- Logical 3-state control of each IOB output buffer is determined by the states of configuration program bits which turn the buffer on or off or select the output buffer 3-state control interconnection (IOB pin .t). When this IOB output control signal is high, a logic 1, the buffer is disabled and the package pin is high impedance. When this IOB output control signal is low, a logic 0, the buffer is enabled and the package pin is active. Inversion of the buffer 3-state control logic sense (output enable) is controlled by an additional configuration program bit.

- Direct or registered output is selectable for each IOB. The register uses a positive-edge, clocked flip-flop. The clock source may be supplied (IOB pin .ok) by either of two metal lines available along each die edge. Each of these lines is driven by an invertible buffer.

- Increased output transition speed can be selected to improve critical timing. Slower transitions reduce capacitive load peak currents of noncritical outputs and minimize system noise.

- A high-impedance pull-up resistor may be used to prevent unused inputs from floating.

## Summary of I/O Options

- Inputs

- —Direct

- —Flip-flop/latch

- -CMOS/TTL threshold (chip inputs)

- -Pull-up resistor/open circuit

- Outputs

- -Direct/registered

- -Inverted/not

- -3-state/on/off

- -Full speed/slew limited

- -3-state/output enable (inverse)

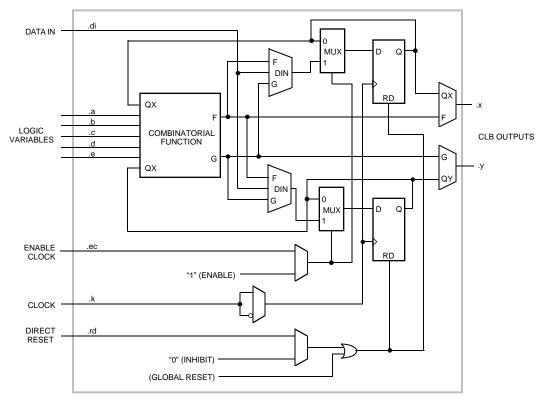

# **Configurable Logic Block**

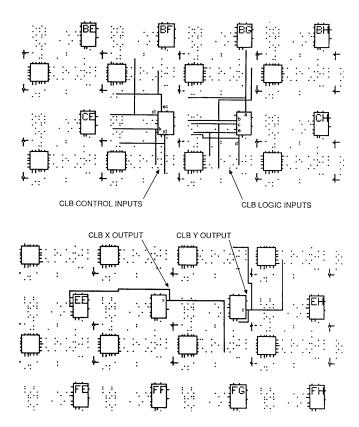

The array of configurable logic blocks (CLBs) provides the functional elements from which the user's logic is constructed. The logic blocks are arranged in a matrix within the perimeter of IOBs. The ATT3020 has 64 such blocks arranged in eight rows and eight columns. The *ORCA* Foundry Development System is used to compile the configuration data for loading into the internal configuration memory to define the operation and interconnection of each block. User definition of CLBs and their interconnecting networks may be done by automatic translation from a schematic capture logic diagram or optionally by installing library or user macros.

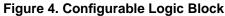

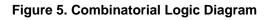

Each CLB has a combinatorial logic section, two flipflops, and an internal control section; see Figure 4 below. There are five logic inputs (.a, .b, .c, .d, and .e); a common clock input (.k); an asynchronous direct reset input (.rd); and an enable clock (.ec). All may be driven from the interconnect resources adjacent to the blocks. Each CLB also has two outputs (.x and .y) which may drive interconnect networks.

Data input for either flip-flop within a CLB is supplied from the function F or G outputs of the combinatorial logic, or the block input, data-in (.di). Both flip-flops in each CLB share the asynchronous reset (.rd) which, when enabled and high, is dominant over clocked inputs. All flip-flops are reset by the active-low chip input, RESET, or during the configuration process.

The flip-flops share the enable clock (.ec) which, when low, recirculates the flip-flops' present states and inhibits response to the data-in or combinatorial function inputs on a CLB. The user may enable these control inputs and select their sources. The user may also select the clock net input (.k), as well as its active sense within each logic block. This programmable inversion eliminates the need to route both phases of a clock signal throughout the device. Flexible routing allows use of common or individual CLB clocking.

The combinatorial logic portion of the logic block uses a 32 x 1 look-up table to implement Boolean functions. Variables selected from the five logic inputs and the two internal block flip-flops are used as table address inputs. The combinatorial propagation delay through the network is independent of the logic function generated and is spike-free for single-input variable changes. This technique can generate two independent logic functions of up to four variables each as shown in Figure 5A, or a single function of five variables as shown in Figure 5B, or some functions of seven variables as shown in Figure 5C.

5-3103(F)

## Configurable Logic Block (continued)

5-3104(F)

- **5A.** Combinatorial Logic Option 1 generates two functions of four variables each. One variable, A, must be common to both functions. The second and third variables can be any choice among B, C, Qx, and Qy. The fourth variable can be either D or E.

- **5B.** Combinatorial Logic Option 2 generates any function of five variables: A, D, E, and two choices among B, C, Qx, Qy.

- **5C.** Combinatorial Logic Option 3 allows variable E to select between two functions of four variables: both have common inputs, A and D, and any choice among B, C, Qx, and Qy for the remaining two variables. Option 3 can then implement some functions of six or seven variables.

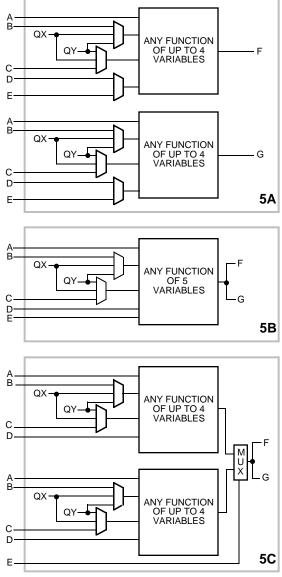

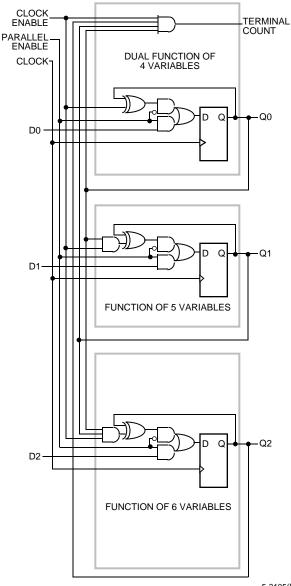

Figure 6 shows a modulo 8 binary counter with parallel enable. It uses one CLB of each type. The partial functions of six or seven variables are implemented by using the input variable (.e) to dynamically select between two functions of four different variables. For the two functions of four variables each, the independent results (F and G) may be used as data inputs to either flip-flop or logic block output. For the single function of five variables and merged functions of six or seven variables, the F and G outputs are identical. Symmetry of the F and G functions and the flip-flops allows the interchange of CLB outputs to optimize routing efficiencies of the networks interconnecting the logic and IOBs.

5-3105(F)

Figure 6. C8BCP Macro

### **Programmable Interconnect**

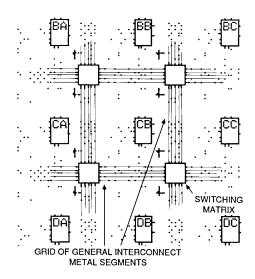

Programmable interconnection resources in the FPGA provide routing paths to connect inputs and outputs of the IOBs and logic blocks into logical networks. Interconnections between blocks are composed from a twolayer grid of metal segments. Specially designed pass transistors, each controlled by a configuration bit, form programmable interconnect points (PIPs) and switching matrices used to implement the necessary connections between selected metal segments and block pins.

Figure 7 is an example of a routed net. The ORCA Foundry Development System provides automatic routing of these interconnections. Interactive routing is also available for design optimization. The inputs of the logic or IOBs are multiplexers which can be programmed to select an input network from the adjacent interconnect segments. Since the switch connections to block inputs are unidirectional (as are block outputs), they are usable only for block input connection and not routing. Figure 8 illustrates routing access to logic block input variables, control inputs, and block outputs.

Three types of metal resources are provided to accommodate various network interconnect requirements:

- General-purpose interconnect

- Direct connection

- Long lines (multiplexed buses and wide-AND gates)

Figure 7. Example of Routing Resources

Figure 8. CLB Input and Output Routing

#### **General-Purpose Interconnect**

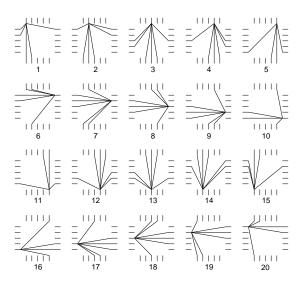

General-purpose interconnect, as shown in Figure 9, consists of a grid of five horizontal and five vertical metal segments located between the rows and columns of logic and IOBs. Each segment is the height or width of a logic block. Switching matrices join the ends of these segments and allow programmed interconnections between the metal grid segments of adjoining rows and columns. The switches of an unprogrammed device are all nonconducting. The connections through the switch matrix may be established by automatic or interactive routing by selecting the desired pairs of matrix pins to be connected or disconnected. The legitimate switching matrix combinations for each pin are indicated in Figure 10.

Special buffers within the general interconnect areas provide periodic signal isolation and restoration for improved performance of lengthy nets. The interconnect buffers are available to propagate signals in either direction on a given general interconnect segment. These bidirectional (bidi) buffers are found adjacent to the switching matrices, above and to the right. The other PIPs adjacent to the matrices are accessed to or from long lines. The development system automatically defines the buffer direction based on the location of the interconnection network source. The delay calculator in the ORCA Foundry Development System automatically calculates and displays the block, interconnect, and buffer delays for any paths selected. Generation of the simulation netlist with a worst-case delay model is also provided by the development system.

Some of the interconnect PIPs are directional, as indicated below:

- ND is a nondirectional interconnection.

- D:H->V is a PIP which drives from a horizontal to a vertical line.

- D:V->H is a PIP which drives from a vertical to a horizontal line.

- D:C->T is a T-PIP which drives from a cross of a T to the tail.

- D:CW is a corner PIP which drives in the clockwise direction.

- P0 indicates the PIP is nonconducting; P1 is on.

Figure 9. FPGA General-Purpose Interconnect

Figure 10. Switch Matrix Interconnection Options

#### **Direct Interconnect**

Direct interconnect (shown in Figure 11) provides the most efficient implementation of networks between adjacent logic or IOBs. Signals routed from block to block using the direct interconnect exhibit minimum interconnect propagation and use no general interconnect resources. For each CLB, the .x output may be connected directly to the .b input of the CLB immediately to its right and to the .c input of the CLB to its left. The .y output can use direct interconnect to drive the .d input of the block immediately above, and the .a input of the block below. Direct interconnect should be used to maximize the speed of high-performance portions of logic. Where logic blocks are adjacent to IOBs, direct connect is provided alternately to the IOB inputs (.i) and outputs (.o) on all four edges of the die. The right edge provides additional direct connects from CLB outputs to adjacent IOBs. Direct interconnections of IOBs with CLBs are shown in Figure 12.

Figure 11. Direct Interconnect

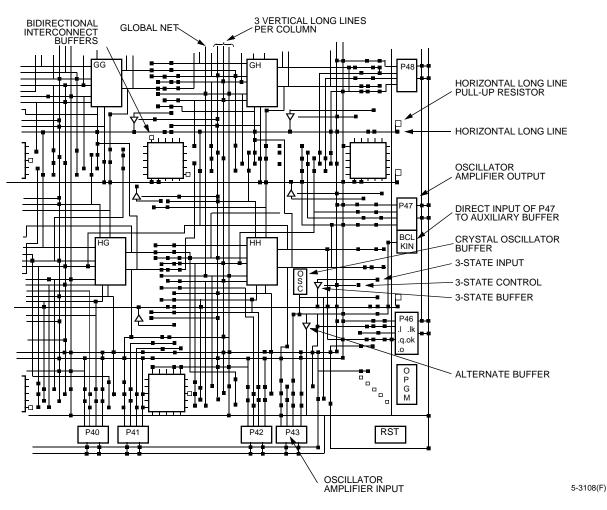

#### Long Lines

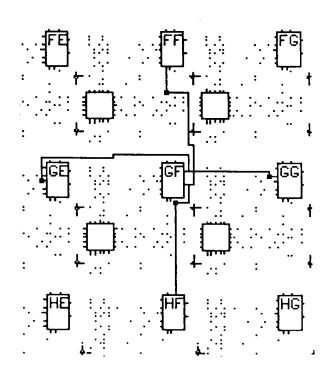

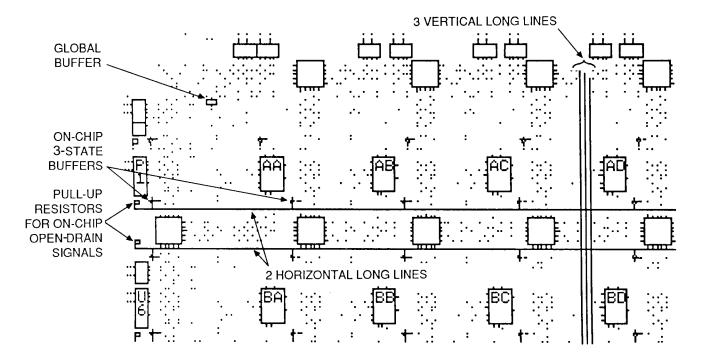

The long lines bypass the switch matrices and are intended primarily for signals which must travel a long distance, or must have minimum skew among multiple destinations. Long lines, shown in Figure 13, run vertically and horizontally the height or width of the interconnect area. Each interconnection column has three vertical long lines, and each interconnection row has two horizontal long lines. Additionally, two long lines are located adjacent to the outer sets of switching matrices. Two vertical long lines in each column are connectable half-length lines, except on the ATT3020, where only the outer long lines serve that function.

Long lines can be driven by a logic block or IOB output on a column-by-column basis. This capability provides a common low-skew control or clock line within each column of logic blocks. Interconnections of these long lines are shown in Figure 14. Isolation buffers are provided at each input to a long line and are enabled automatically by the development system when a connection is made.

Figure 13. Horizontal and Vertical Long Lines in the FPGA

A buffer in the upper left corner of the FPGA chip drives a global net which is available to all .k inputs of logic blocks. Using the global buffer for a clock signal provides a skew-free, high fan-out, synchronized clock for use at any or all of the I/O and logic blocks. Configuration bits for the .k input to each logic block can select this global line, or another routing resource, as the clock source for its flip-flops. This net may also be programmed to drive the die edge clock lines for IOB use. An enhanced speed, CMOS threshold, offers direct access to this buffer and is available at the second pad from the top of the left die edge.

A buffer in the lower right corner of the array drives a horizontal long line that can drive programmed connections to a vertical long line in each interconnection column. This alternate buffer also has low skew and high fan-out. The network formed by this alternate buffer's long lines can be selected to drive the .k inputs of the logic blocks. CMOS threshold, high-speed access to this buffer is available from the third pad from the bottom of the right die edge.

\* FOUR OUTER LONG LINES ARE

#### **Internal Buses**

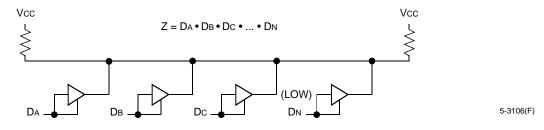

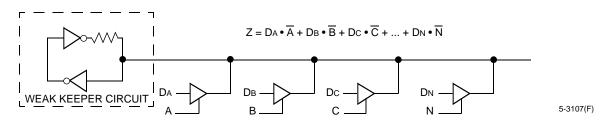

A pair of 3-state buffers is located adjacent to each CLB. These buffers allow logic to drive the horizontal long lines. Logical operation of the 3-state buffer controls allows them to implement wide multiplexing functions. Any 3-state buffer input can be selected as drive for the horizontal long line bus by applying a low logic level on its 3-state control line (see Figure 15A). The user is required to avoid contention that can result from multiple drivers with opposing logic levels. Control of the 3-state input by the same signal that drives the buffer input creates an open-drain wired-AND function. A logical high on both buffer inputs creates a high impedance which represents no contention. A logical low enables the buffer to drive the long line low (see Figure 15B). Pull-up resistors are available at each end of the long line to provide a high output when all connected buffers are nonconducting. This forms fast, wide gating functions. When data drives the inputs and separate signals drive the 3-state control lines, these buffers form multiplexers (3-state buses). In this case, care must be used to prevent contention through multiple active buffers of conflicting levels on a common line. Figure 16 shows 3-state buffers, long lines, and pull-up resistors.

| CONNECTIBLE HALF-LENG | I/O BLOCK CLOCK NETS |                          |

|-----------------------|----------------------|--------------------------|

|                       |                      | (2 PER DIE EDGE)         |

|                       |                      |                          |

|                       |                      | HORIZONTAL<br>LONG LINES |

|                       |                      |                          |

|                       |                      | >3-STATE<br>BUFFERS      |

|                       |                      |                          |

|                       | 6.6.7                |                          |

|                       |                      |                          |

|                       | e e e                |                          |

|                       |                      |                          |

Figure 14. Programmable Interconnection of Long Lines

Figure 15A. 3-State Buffers Implement a Wired-AND Function

Figure 15B. 3-State Buffers Implement a Multiplexer

Figure 16. Lower-Right Corner of ATT3020

### **Crystal Oscillator**

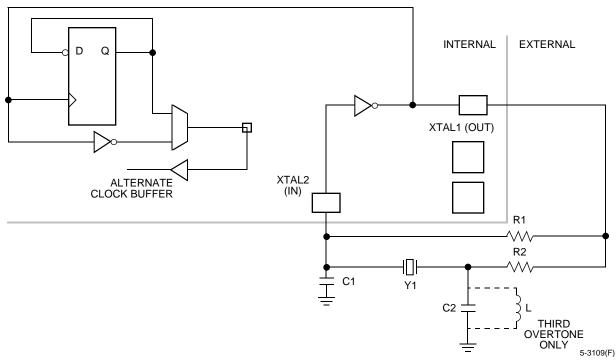

Figure 16 shows the location of an internal high-speed inverting amplifier which may be used to implement an on-chip crystal oscillator. It is associated with the auxiliary buffer in the lower right corner of the die. When the oscillator is configured and connected as a signal source, two special user IOBs are also configured to connect the oscillator amplifier with external crystal oscillator components as shown in Figure 17. A divideby-two option is available to ensure symmetry. The oscillator circuit becomes active before configuration is complete in order to allow the oscillator to stabilize. Actual internal connection is delayed until completion of configuration. In Figure 17, the feedback resistor, R1, between output and input biases the amplifier at threshold. The value should be as large as is practical

to minimize loading of the crystal. The inversion of the amplifier, together with the R-C networks and an AT cut series resonant crystal, produces the 360° phase shift of the Pierce oscillator. A series resistor, R2, may be included to add to the amplifier output impedance when needed for phase shift control or crystal resistance matching, or to limit the amplifier input swing to control clipping at large amplitudes. Excess feedback voltage may be corrected by the ratio of C2/C1. The amplifier is designed to be used from 1 MHz to one-half the specified CLB toggle frequency. Use at frequencies below 1 MHz may require individual characterization with respect to a series resistance. Crystal oscillators above 20 MHz generally require a crystal which operates in a third overtone mode, where the fundamental frequency must be suppressed by an inductor across C2. When the oscillator inverter is not used, these IOBs and their package pins are available for general user I/O.

Suggested component values:

R1-0.5 M to 1 M

R2—0 k to 1 k (may be required for low frequency, phase shift, and/or compensation level for Crystal Q) C1, C2—10 pF to 40 pF

Y1—1 MHz to 20 MHz AT cut series resonant

| Din         | 44-Pin | 68-Pin | 84-Pin | 100 | -Pin | 132-Pin | 144-Pin | 160-Pin | 175-Pin | 208-Pin |

|-------------|--------|--------|--------|-----|------|---------|---------|---------|---------|---------|

| Pin         | PLCC   | PLCC   | PLCC   | QFP | TQFP | PPGA    | TQFP    | QFP     | PPGA    | SQFP    |

| XTAL1 (OUT) | 30     | 47     | 57     | 82  | 79   | P13     | 75      | 82      | T14     | 110     |

| XTAL2 (IN)  | 26     | 43     | 53     | 76  | 73   | M13     | 69      | 76      | P15     | 100     |

Figure 17. Crystal Oscillator Inverter

# Configuration

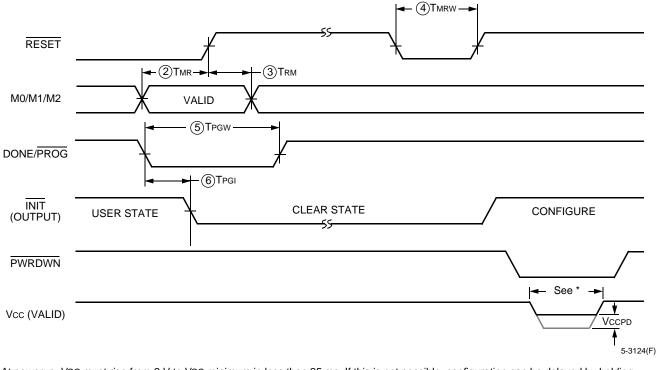

#### **Initialization Phase**

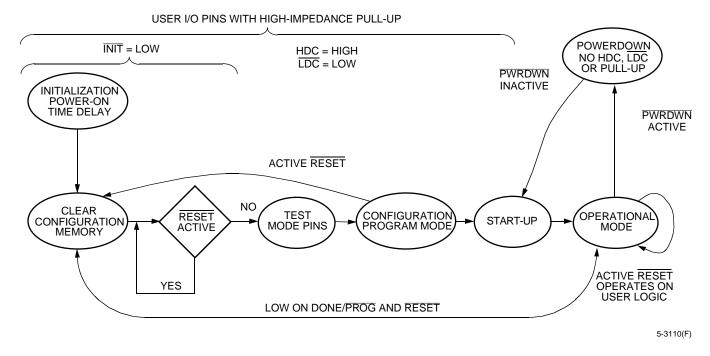

An internal power-on-reset circuit is triggered when power is applied. When Vcc reaches the voltage where portions of the FPGA begin to operate (2.5 V to 3 V), the programmable I/O output buffers are disabled and a high-impedance pull-up resistor is provided for the user I/O pins. A time-out delay is initiated to allow the power supply voltage to stabilize. During this time, the powerdown mode is inhibited. The initialization state time-out (about 11 ms to 33 ms) is determined by a 14-bit counter driven by a self-generated, internal timer. This nominal 1 MHz timer is subject to variations with process, temperature, and power supply over the range of 0.5 MHz to 1.5 MHz. As shown in Table 2, five configuration mode choices are available, as determined by the input levels of three mode pins: M0, M1, and M2.

#### **Table 2. Configuration Modes**

| MO | M1 | M2 | Clock   | Mode       | Data                                  |

|----|----|----|---------|------------|---------------------------------------|

| 0  | 0  | 0  | Active  | Master     | Bit Serial                            |

| 0  | 0  | 1  | Active  | Master     | Byte Wide<br>(Address = 0000<br>up)   |

| 0  | 1  | 0  | _       | Reserved   | —                                     |

| 0  | 1  | 1  | Active  | Master     | Byte Wide<br>(Address = FFFF<br>down) |

| 1  | 0  | 0  | _       | Reserved   | —                                     |

| 1  | 0  | 1  | Active  | Peripheral | Byte Wide                             |

| 1  | 1  | 0  | _       | Reserved   | —                                     |

| 1  | 1  | 1  | Passive | Slave      | Bit Serial                            |

In master configuration mode, the FPGA becomes the source of configuration clock (CCLK). Beginning configuration of devices using peripheral or slave modes must be delayed long enough for their initialization to be completed. An FPGA with mode lines selecting a master configuration mode extends its initialization state using four times the delay (43 ms to 130 ms) to ensure that all daisy-chained slave devices it may be driving will be ready, even if the master is very fast and the slave(s), very slow (see Figure 18). At the end of initialization, the FPGA enters the clear state where it clears configuration memory. The active-low, opendrain initialization signal INIT indicates when the initialization and clear states are complete. The FPGA tests for the absence of an external active-low RESET before it makes a final sample of the mode lines and enters the configuration state. An external wired-AND of one or more INIT pins can be used to control configuration by the assertion of the active-low RESET of a master mode device or to signal a processor that the FPGAs are not yet initialized.

If a configuration has begun, a reassertion of RESET for a minimum of three internal timer cycles will be recognized and the FPGA will initiate an abort, returning to the clear state to clear the partially loaded configuration memory words. The FPGA will then resample RESET and the mode lines before reentering the configuration state.

A reprogram is initiated when a configured FPGA senses a high-to-low transition on the DONE/PROG package pin. The FPGA returns to the clear state where configuration memory is cleared and mode lines resampled, as for an aborted configuration. The complete configuration program is cleared and loaded during each configuration program cycle.

Figure 18. State Diagram of Configuration Process for Powerup and Reprogram

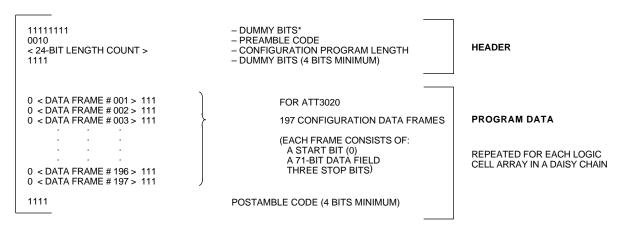

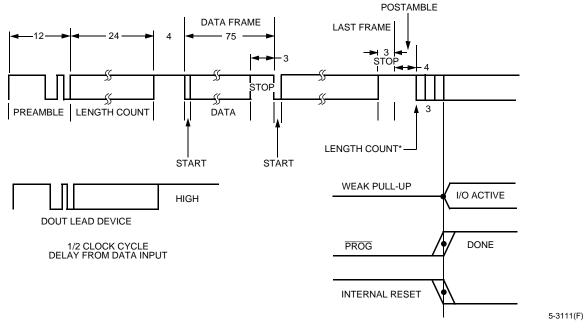

Length count control allows a system of multiple FPGAs in assorted sizes to begin operation in a synchronized fashion. The configuration program generated by the ORCA Foundry Development System begins with a preamble of 111111110010 (binary), followed by a 24-bit length count representing the total number of configuration clocks needed to complete loading of the configuration program(s). The data framing is shown in Figure 19. All FPGAs connected in series read and shift preamble and length count in (on positive) and out (on negative) CCLK edges. An FPGA which has received the preamble and length count then presents a HIGH data out until it has intercepted the appropriate number of data frames. When the configuration program memory of an FPGA is full and the length count does not compare, the FPGA shifts any additional data through, as it did for preamble and length count.

When the FPGA configuration memory is full and the length count compares, the FPGA will execute a synchronous start-up sequence and become operational (see Figure 20 on page 20). Two CCLK cycles after the completion of loading configuration data, the user I/O pins are enabled as configured. As selected in *ORCA* Foundry, the internal user-logic reset is released either one clock cycle before or after the I/O pins become active. A similar timing selection is programmable for the DONE/PROG output signal. DONE/PROG may also be programmed to be an open drain or include a pull-up resistor to accommodate wired-ANDing. The high during configuration (HDC) and low during configuration (LDC) are two user I/O pins which are driven active when an FPGA is in initialization, clear, or configure states. These signals and DONE/ PROG provide for control of external logic signals such as reset, bus enable, or PROM enable during configuration.

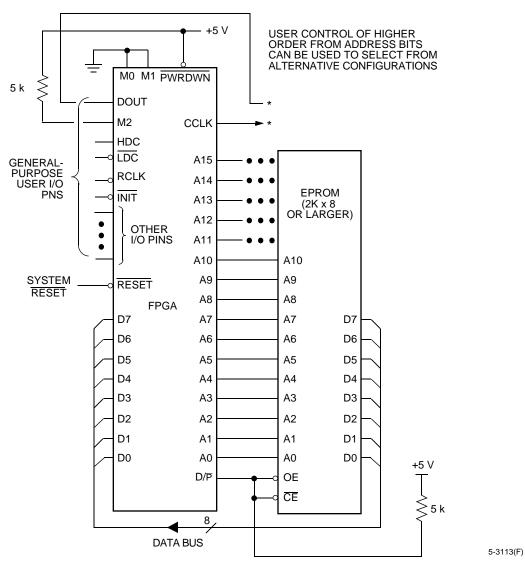

For parallel master configuration modes, these signals provide PROM enable control and allow the data pins to be shared with user logic signals.

User I/O inputs can be programmed to be either TTL or CMOS compatible thresholds. At powerup, all inputs have TTL thresholds and can change to CMOS thresholds at the completion of configuration, if the user has selected CMOS thresholds. The threshold of PWRDWN and the direct clock inputs are fixed at a CMOS level.

If the crystal oscillator is used, it will begin operation before configuration is complete to allow time for stabilization before it is connected to the internal circuitry.

#### **Configuration Data**

Configuration data to define the function and interconnection within an FPGA are loaded from an external storage at powerup and on a reprogram signal. Several methods of automatic and controlled loading of the required data are available. Logic levels applied to mode selection pins at the start of configuration time determine the method to be used (see Table 2). The data may be either bit-serial or byte-parallel, depending on the configuration mode. Various Lucent programmable gate arrays have different sizes and numbers of data frames. For the ATT3020, configuration requires 14779 bits for each device, arranged in 197 data frames. An additional 40 bits are used in the header (see Figure 20).

\* The FPGA devices require four dummy bits minimum.

#### Figure 19. Internal Configuration Data Structure

#### Table 3. ATT3000 Device Configuration Data

| Device                                                   | ATT3020       | ATT3030          | ATT3042          | ATT3064          | ATT3090          |

|----------------------------------------------------------|---------------|------------------|------------------|------------------|------------------|

| Gates                                                    | 1500          | 2000             | 3000             | 4500             | 6000             |

| CLBs<br>(row x column)                                   | 64<br>(8 x 8) | 100<br>(10 x 10) | 144<br>(12 x 12) | 224<br>(16 x 14) | 320<br>(20 x 16) |

| IOBs                                                     | 64            | 80               | 96               | 120              | 144              |

| Flip-flops                                               | 256           | 360              | 480              | 688              | 928              |

| Bits-per-frame<br>(with 1 start/3 stop)                  | 75            | 92               | 108              | 140              | 172              |

| Frames                                                   | 197           | 241              | 285              | 329              | 373              |

| Program Data =<br>Bits * Frames + 4<br>(excludes header) | 14779         | 22176            | 30784            | 46064            | 64160            |

| PROM Size (bits) =<br>Program Data<br>+ 40-bit Headers   | 14819         | 22216            | 30824            | 46104            | 64200            |

Note: The length count produced by the bit stream generation program = [(40-bit preamble + sum of program data + 1 per daisy-chain device) rounded up to a multiple of 8] – (2 K 4), where K is a function of DONE and RESET timing selected. An additional 8 is added if the roundup increment is less than K. K additional clocks are needed to complete start-up after length count is reached.

\* The configuration data consists of a composite 40-bit preamble/length count, followed by one or more concatenated FPGA programs, separated by 4-bit postambles. An additional final postamble bit is added for each slave device, and the result rounded up to byte boundary. The length count is two less than the number of resulting bits. Timing of the assertion of DONE and termination of the internal RESET may each be programmed to occur one cycle before or after the I/O outputs become active.

#### Figure 20. FPGA Configuration and Start-Up

The specific data format for each device is produced by the bit stream generation program, and one or more of these files can then be combined and appended to a length count preamble and be transformed into a PROM format file by the PROM generation program of the *ORCA* Foundry Development System. The tie option of the bit stream generation program defines output levels of unused blocks of a design and connects these to unused routing resources. This prevents indeterminate levels which might produce parasitic supply currents. This tie option can be omitted for quick breadboard iterations where a few additional mA of ICC are acceptable.

The configuration bit stream begins with high preamble bits, a 4-bit preamble code, and a 24-bit length count. When configuration is initiated, a counter in the FPGA is set to 0 and begins to count the total number of configuration clock cycles applied to the device. As each configuration data frame is supplied to the FPGA, it is internally assembled into a data word. As each data word is completely assembled, it is loaded in parallel into one word of the internal configuration memory array. The configuration loading process is complete when the current length count equals the loaded length count and the required configuration program data frames have been written. Internal user flip-flops are held reset during configuration.

Two user-programmable pins are defined in the unconfigured FPGA: high during configuration (HDC) and low during configuration (LDC), and DONE/PROG may be used as external control signals during configuration. In master mode configurations, it is convenient to use LDC as an active-low EPROM chip enable. After the last configuration data bit is loaded and the length count compares, the user I/O pins become active. Options in the bit stream generation program allow timing choices of one clock earlier or later for the timing of the end of the internal logic reset and the assertion of the DONE signal. The open-drain DONE/PROG output can be AND-tied with multiple FPGAs and used as an activehigh READY, an active-low PROM enable, or a RESET to other portions of the system. The state diagram of Figure 18 illustrates the configuration process.

# **Configuration Modes**

#### **Master Mode**

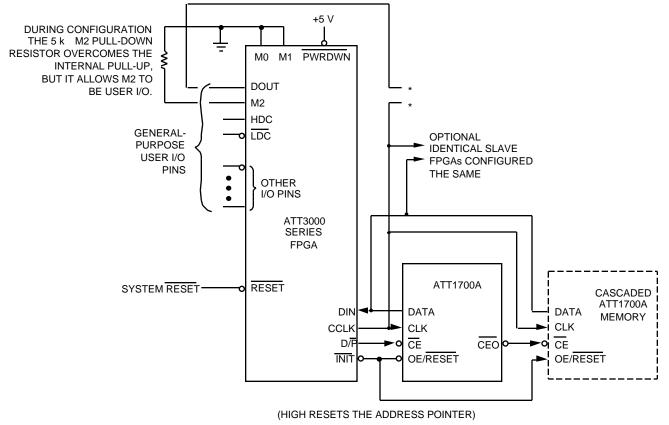

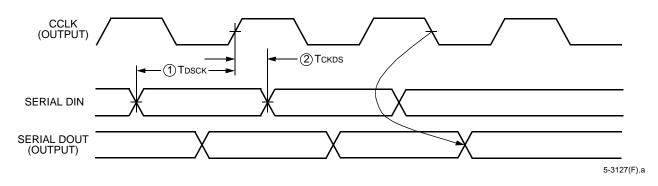

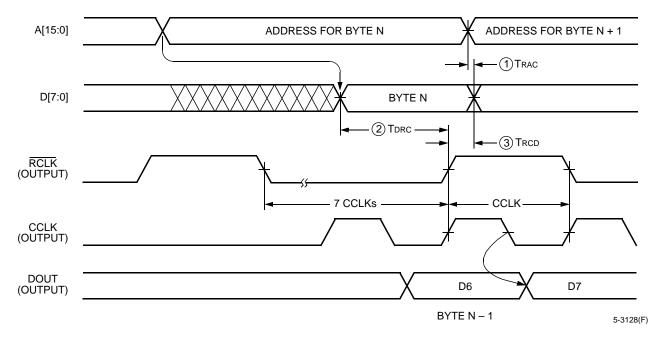

In master mode, the FPGA automatically loads configuration data from an external memory device. There are three master modes which use the internal timing source to supply the configuration clock (CCLK) to time the incoming data. Serial master mode uses serial configuration data supplied to data-in (DIN) from a synchronous serial source such as the serial configuration PROM shown in Figure 21. Parallel master low and master high modes automatically use parallel data supplied to the D[7:0] pins in response to the 16-bit address generated by the FPGA. Figure 22 shows an example of the parallel master mode connections required. The FPGA HEX starting address is 0000 and increments for master low mode, and it is FFFF and decrements for master high mode. These two modes provide address compatibility with microprocessors which begin execution from opposite ends of memory.

For master high or low, data bytes are read in parallel by each read clock (RCLK) and internally serialized by the configuration clock. As each data byte is read, the least significant bit of the next byte, D0, becomes the next bit in the internal serial configuration word. One master mode FPGA can be used to interface the configuration program-store, and pass additional concatenated configuration data to additional FPGAs in a serial daisy-chain fashion. CCLK is provided for the slaved devices, and their serialized data is supplied from DOUT to DIN, DOUT to DIN, etc.

5-3112(C)

Note: The serial configuration PROM supports automatic loading of configuration programs up to 36/64/128 Kbits. Multiple devices can be cascaded to support additional FPGAs. An early DONE inhibits the data output one CCLK cycle before the FPGA I/O becomes active.

Figure 21. Master Serial Mode

Figure 22. Master Parallel Mode

#### **Peripheral Mode**

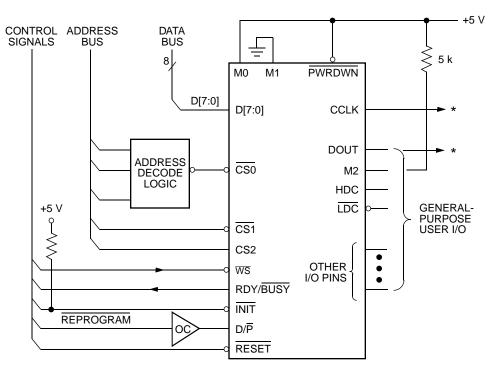

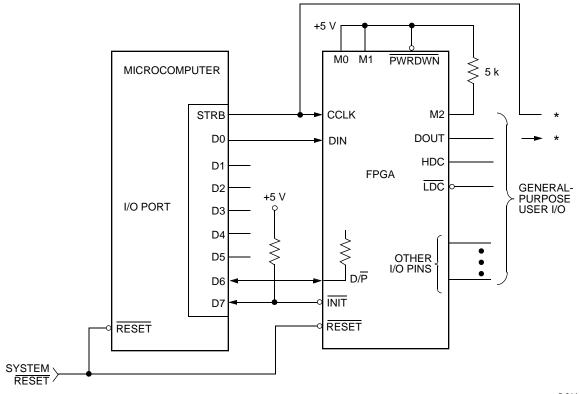

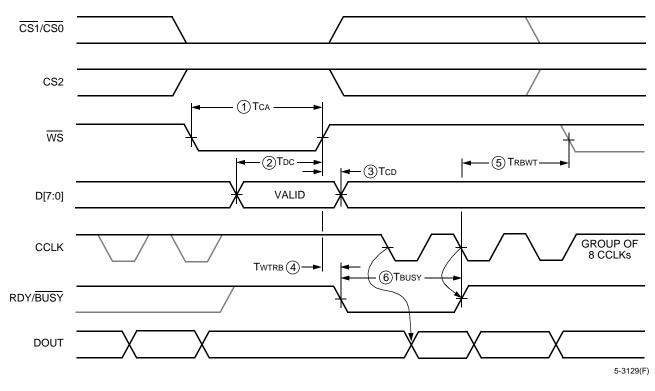

Peripheral mode provides a simplified interface through which the device may be loaded byte-wide, as a processor peripheral. Figure 23 shows the peripheral mode connections. Processor write cycles are decoded from the common assertion of the active-low write strobe (WS), and two active-low and one active-high chip selects (CS0, CS1, CS2). If all of these signals are not available, the unused inputs should be driven to their respective active levels. The FPGA will accept 1 byte of configuration data on the D[7:0] inputs for each selected processor write cycle. Each byte of data is loaded into a buffer register. The FPGA generates a CCLK from the internal timing generator and serializes the parallel input data for internal framing or for succeeding slaves on data out (DOUT). An output HIGH on READY/BUSY pin indicates the completion of loading for each byte when the input register is ready for a new byte. As with master modes, peripheral mode may also be used as a lead device for a daisy-chain of slave devices.

5-3114(F)

Figure 23. Peripheral Mode

#### **Slave Mode**

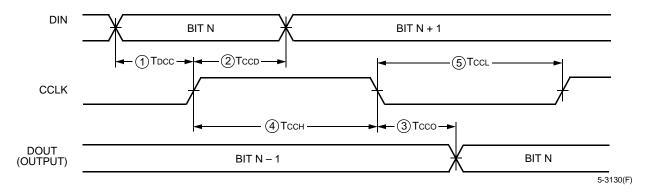

Slave mode provides a simple interface for loading the FPGA configuration as shown in Figure 24. Serial data is supplied in conjunction with a synchronizing input clock. Most slave mode applications are in daisy-chain configurations in which the data input is supplied by the previous FPGA's data out, while the clock is supplied by a lead device in master or peripheral mode. Data may also be supplied by a processor or other special circuits.

5-3115(F)

Figure 24. Slave Mode

### **Daisy Chain**

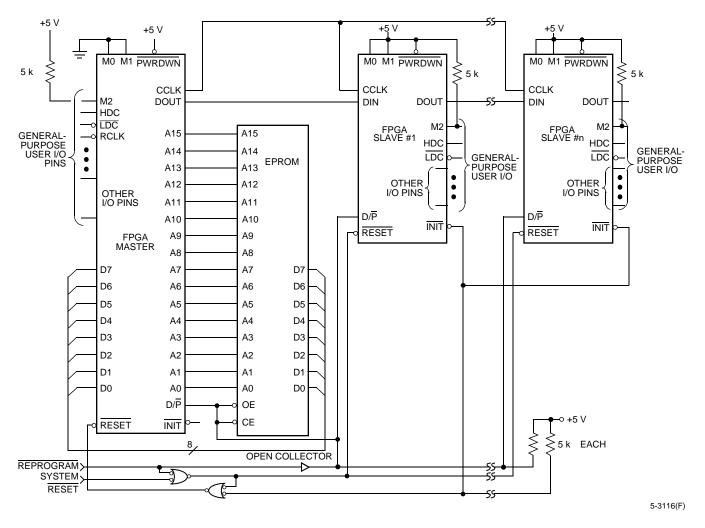

The ORCA Foundry for ATT3000 Development System is used to create a composite configuration bit stream for selected FPGAs including a preamble, a length count for the total bit stream, multiple concatenated data programs, a postamble, plus an additional fill bit per device in the serial chain. After loading and passing on the preamble and length count to a possible daisy chain, a lead device will load its configuration data frames while providing a high DOUT to possible downstream devices as shown in Figure 25. Loading continues while the lead device has received its configuration program and the current length count has not reached the full value. Additional data is passed through the lead device and appears on the data out (DOUT) pin in serial form. The lead device also generates the CCLK to synchronize the serial output data and data in of downstream FPGAs. Data is read in on DIN of slave devices by the positive edge of CCLK and shifted out the DOUT on the negative edge of CCLK. A parallel master mode device uses its internal timing generator to produce an internal CCLK of eight times its EPROM address rate, while a peripheral mode device produces a burst of eight CCLKs for each chip select and writestrobe cycle. The internal timing generator continues to operate for general timing and synchronization of inputs in all modes.

Figure 25. Master Mode with Daisy-Chained Slave Mode Devices

## **Special Configuration Functions**

The configuration data includes control over several special functions in addition to the normal user logic functions and interconnects:

- Input thresholds

- Readback enable

- DONE pull-up resistor

- DONE timing

- RESET timing

- Oscillator frequency divided by two

Each of these functions is controlled by configuration data bits which are selected as part of the normal development system bit stream generation process.

#### **Input Thresholds**

Prior to the completion of configuration, all FPGA input thresholds are TTL compatible. Upon completion of configuration, the input thresholds become either TTL or CMOS compatible as programmed. The use of the TTL threshold option requires some additional supply current for threshold shifting. The exception is the threshold of the PWRDWN input and direct clocks which always have a CMOS input. Prior to the completion of configuration, the user I/O pins each have a highimpedance pull-up. The configuration program can be used to enable the IOB pull-up resistors in the operational mode to act either as an input load or to avoid a floating input on an otherwise unused pin.

#### Readback

The contents of an FPGA may be read back if it has been programmed with a bit stream in which the readback option has been enabled. Readback may be used for verification of configuration and as a method for determining the state of internal logic nodes. There are three options in generating the configuration bit stream:

- Never will inhibit the readback capability.

- One-time will inhibit readback after one readback has been executed to verify the configuration.

- On-command will allow unrestricted use of readback.

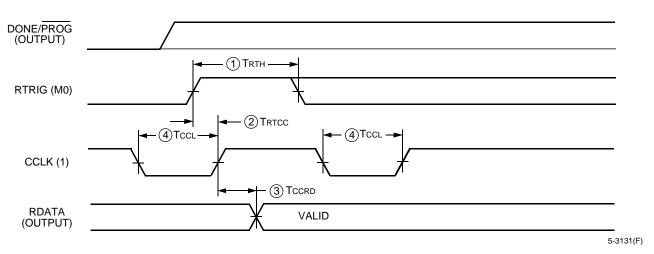

Readback is accomplished without the use of any of the user I/O pins; only M0, M1, and CCLK are used. The initiation of readback is produced by a low-to-high transition of the M0/RTRIG (read trigger) pin. Once the readback command has been given, the input CCLK is driven by external logic to read back each data bit in a format similar to loading. After two dummy bits, the first data frame is shifted out on the M1/RDATA (read data) pin. The logic polarity of the readback data is always inverted, such that a zero in configuration becomes a one in readback and vice versa. Each readback frame has one start bit and one stop bit per frame (configuration writes at least 3 stop bits per frame). All data frames must be read back to complete the process and return the mode select and CCLK pins to their normal functions.

The readback data includes the current state of each internal logic block storage element, and the state of the input (.i and .ri) connection pins on each IOB. The data is imbedded into unused configuration bit positions during readback. This state information is used by the FPGA development system in-circuit verifier to provide visibility into the internal operation of the logic while the system is operating. To read back a uniform time sample of all storage elements, it may be necessary to inhibit the system clock.

# Special Configuration Functions (continued)

#### Reprogram

The FPGA configuration memory can be rewritten while the device is operating in the user's system. To initiate a reprogramming cycle, the dual-function package pin DONE/PROG must be given a high-to-low transition. To reduce sensitivity to noise, the input signal is filtered for two cycles of the FPGA's internal timing generator. When reprogram begins, the user-programmable I/O output buffers are disabled and high-impedance pull-ups are provided for the package pins. The device returns to the clear state and clears the configuration memory before it prompts INITIALIZED. Since this clear operation uses chip-individual internal timing, the master might complete the clear operation and then start configuration before the slave has completed the clear operation. To avoid this, wire-AND the slave INIT pins and use them to force a RESET on the master (see Figure 25). Reprogram control is often implemented by using an external open-collector driver which pulls DONE/PROG low. Once it recognizes a stable request, the FPGA will hold a low until the new configuration has been completed. Even if the reprogram request is externally held low beyond the configuration period, the FPGA will begin operation upon completion of configuration.

## **DONE Pull-Up**

DONE/PROG is an open-drain I/O pin that indicates the FPGA is in the operational state. An optional internal pull-up resistor can be enabled by the user of the development system when the bit stream generation program is executed. The DONE/PROG pins of multiple FPGAs in a daisy chain may be connected together to indicate that all are DONE or to direct them all to reprogram.

## **DONE** Timing

The timing of the DONE status signal can be controlled by a selection in the bit stream generation program to occur a CCLK cycle before, or after, the timing of outputs being activated (see Figure 20). This facilitates control of external functions, such as a PROM enable or holding a system in a wait-state.

## **RESET Timing**

As with DONE timing, the timing of the release of the internal RESET can be controlled by a selection in the bit stream generation program to occur a CCLK cycle before, or after, the timing of outputs being enabled (see Figure 20). This reset maintains all user-programmable flip-flops and latches in a zero state during configuration.

## **Crystal Oscillator Division**

A selection in the bit stream generation program allows the user to incorporate a dedicated divide-by-two flipflop in the crystal oscillator function. This provides higher assurance of a symmetrical timing signal. Although the frequency stability of crystal oscillators is high, the symmetry of the waveform can be affected by bias or feedback drive.

#### Performance

#### **Device Performance**

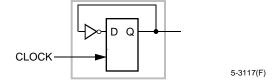

The high performance of the FPGA is due in part to the manufacturing process, which is similar to that used for high-speed CMOS static memories. Performance can be measured in terms of minimum propagation times for logic elements. The parameter which traditionally describes the overall performance of a gate array is the toggle frequency of a flip-flop. The configuration for determining the toggle performance of the FPGA is shown in Figure 26. The flip-flop output Q is fed back through the combinatorial logic as Q to form the toggle flip-flop.

Figure 26. Toggle Flip-Flop

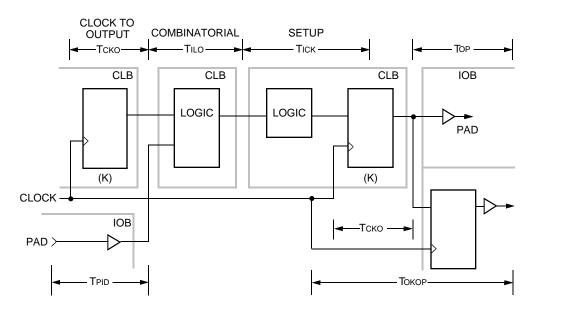

FPGA performance is determined by the timing of critical paths, including both the fixed timing for the logic and storage elements in that path, and the timing associated with the routing of the network. Examples of internal worst-case timing are included in the performance data to allow the user to make the best use of the capabilities of the device. The ORCA Foundry Development System timing calculator or ORCA Foundry-generated simulation models should be used to calculate worst-case paths by using actual impedance and loading information.

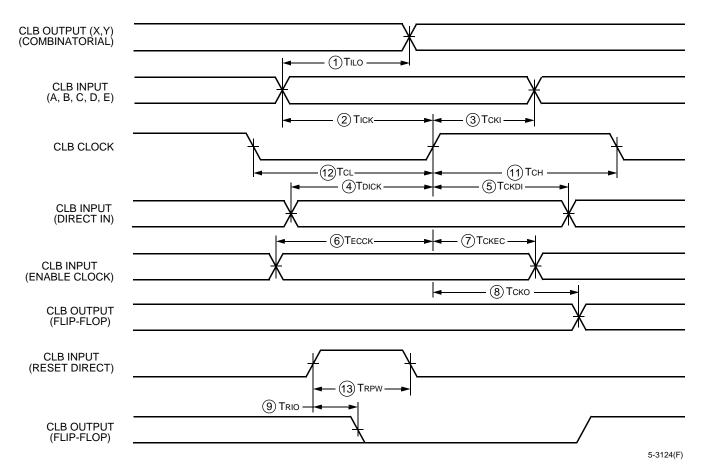

Figure 27 shows a variety of elements which are involved in determining system performance. Table 20 gives the parameter values for the different speed grades. Actual measurement of internal timing is not practical, and often only the sum of component timing is relevant as in the case of input to output. The relationship between input and output timing is arbitrary, and only the total determines performance.

Timing components of internal functions may be determined by the measurement of differences at the pins of the package. A synchronous logic function which involves a clock to block-output and a block-input to clock setup is capable of higher-speed operation than a logic configuration of two synchronous blocks with an extra combinatorial block level between them. System clock rates to 60% of the toggle frequency are practical for logic in which an extra combinatorial level is located between synchronized blocks. This allows implementation of functions of up to 25 variables. The use of the wired-AND is also available for wide, high-speed functions.

5-3118(F)

Figure 27. Examples of Primary Block Speed Factors

#### Performance (continued)

#### Logic Block Performance

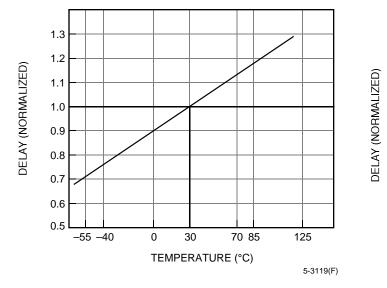

Logic block performance is expressed as the propagation time from the interconnect point at the input of the combinatorial logic to the output of the block in the interconnect area. Combinatorial performance is independent of the specific logic function because of the table look-up based implementation. Timing is different when the combinatorial logic is used in conjunction with the storage element. For the combinatorial logic function driving the data input of the storage element, the critical timing is data setup relative to the clock edge provided to the flip-flop element. The delay from the clock source to the output of the logic block is critical in the timing of signals produced by storage elements. Loading of a logic block output is limited only by the resulting propagation delay of the larger interconnect network. Speed performance of the logic block is a function of supply voltage and temperature (see Figures 28 and 29).

#### **Interconnect Performance**

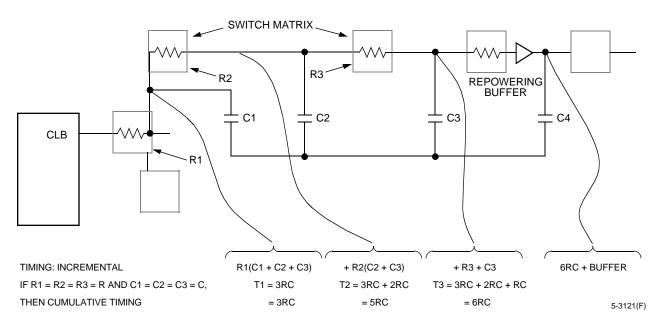

Interconnect performance depends on the routing resource used to implement the signal path. As discussed earlier, direct interconnect from block to block provides a fast path for a signal. The single metal segment used for long lines exhibits low resistance from end to end, but relatively high capacitance. Signals driven through a programmable switch will have the additional impedance of the switch added to their normal drive impedance.

General-purpose interconnect performance depends on the number of switches and segments used, the presence of the bidirectional repowering buffers, and the overall loading on the signal path at all points along the path. In calculating the worst-case timing for a general interconnect path, the timing calculator portion of the *ORCA* Foundry Development System accounts for all of these elements.

As an approximation, interconnect timing is proportional to the summation of totals of local metal segments beyond each programmable switch. In effect, the time is a sum of R-C time each approximated by an R times the total C it drives. The R of the switch and the C of the interconnect are functions of the particular device performance grade.

For a string of three local interconnects, the approximate time at the first segment after the first switch resistance would be three units—an additional two units after the next switch plus an additional unit after the last switch in the chain. The interconnect R-C chain terminates at each repowering buffer. The capacitance of the actual block inputs is not significant; the capacitance is in the interconnect metal and switches. Figure 30 illustrates this.

1.2

1.1

1.0

0.9

4.0

### Performance (continued)

Figure 29. Speed Performance of a CMOS Device

5.0

Vcc

5.5

6.0

5-3120(F)

4.5

Figure 30. Interconnection Timing Example

#### Power

#### **Power Distribution**

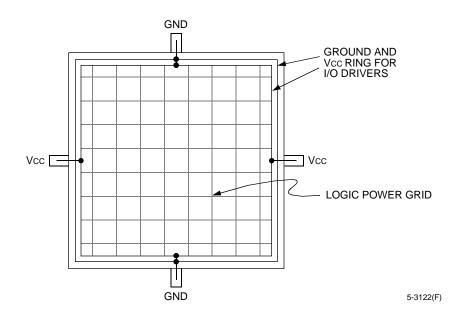

Power for the FPGA is distributed through a grid to achieve high noise immunity and isolation between logic and I/O. Inside the FPGA, a dedicated Vcc and ground ring surrounding the logic array provides power to the I/O drivers (see Figure 31 below). An independent matrix of Vcc and ground lines supplies the interior logic of the device. This power distribution grid provides a stable supply and ground for all internal logic, provided that the external package power pins are all connected and appropriately decoupled. Typically, a 0.1  $\mu$ F capacitor connected near the Vcc and ground pins of the package will provide adequate decoupling.

Output buffers which drive the specified 4 mA loads under worst-case conditions may drive 25 to 30 times this amount under best-case process conditions. Noise can be reduced by minimizing external load capacitance and reducing simultaneous output transitions in the same direction. It may also be beneficial to locate heavily loaded output buffers near the ground pads. The IOB output buffers have a slew-limited mode which should be used where output rise and fall times are not speed critical.

Slew-limited outputs maintain their dc drive capability but generate less external reflections and internal noise. More than 32 fast outputs should not be switching in the same direction simultaneously.

Figure 31. FPGA Power Distribution

#### Power (continued)

#### **Power Dissipation**

The FPGA exhibits the low power consumption characteristic of CMOS ICs. The configuration option of TTL chip input threshold requires power for the threshold reference. The power required by the static memory cells that hold the configuration data is very low and may be maintained in a powerdown mode.

Typically, most of the power dissipation is produced by external capacitive loads on the output buffers. This load and frequency dependent power is  $25 \,\mu$ W/pF/MHz per output. Another component of I/O power is the dc loading on each output pin by devices driven by the FPGA.

Internal power dissipation is a function of the number and size of the nodes, and the frequency at which they change. In an FPGA, the fraction of nodes changing on a given clock is typically low (10% to 20%). For example, in a large binary counter, the average clock cycle produces changes equal to one CLB output at the clock frequency. Typical global clock buffer power is between 1.7 mW/MHz for the ATT3020 and 3.5 mW/ MHz for the ATT3090. The internal capacitive load is more a function of interconnect than fan-out. With a typical load of three general interconnect segments, each configurable logic block output requires about 0.22 mW/MHz of its output frequency:

Total Power = Vcc + Icco + External (dc + Capacitive) + Internal (CLB + IOB + Long Line + Pull-up) Because the control storage of the FPGA is CMOS static memory, its cells require a very low standby current for data retention. In some systems, this low data retention current characteristic can be used as a method of preserving configurations in the event of a primary power loss. The FPGA has built-in powerdown logic which, when activated, will disable normal operation of the device and retain only the configuration data. All internal operation is suspended and output buffers are placed in their high-impedance state with no pullups. Powerdown data retention is possible with a simple battery backup circuit, because the power requirement is extremely low. For retention at 2.4 V, the required current is typically on the order of 50 nA.

To force the FPGA into the powerdown state, the user must pull the PWRDWN pin low and continue to supply a retention voltage to the VCC pins of the package. When normal power is restored, VCC is elevated to its normal operating voltage and PWRDWN is returned to a high. The FPGA resumes operation with the same internal sequence that occurs at the conclusion of configuration. Internal I/O and logic block storage elements will be reset, the outputs will become enabled, and the DONE/PROG pin will be released. No configuration programming is involved.

When the power supply is removed from a CMOS device, it is possible to supply some power from an input signal. The conventional electrostatic input protection is implemented with diodes to the supply and ground. A positive voltage applied to an I/O will cause the positive protection diode to conduct and drive the power pin. This condition can produce invalid power conditions and should be avoided. A large series resistor might be used to limit the current or a bipolar buffer may be used to isolate the input signal.

## **Pin Information**

#### Table 4. Permanently Dedicated Pins

| Symbol        | Name/Description                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vcc           | Two to eight (depending on package type) connections to the nominal +5 V supply voltage. All must be connected.                                                                                                                                                                                                                                                                                                           |

| GND           | Two to eight (depending on package type) connections to ground. All must be connected.                                                                                                                                                                                                                                                                                                                                    |

| PWRDWN        | A low on this CMOS compatible input stops all internal activity to minimize Vcc power, and puts all output buffers in a high-impedance state; configuration is retained. When the PWRDWN pin returns high, the device returns to operation with the same sequence of buffer enable and DONE/PROG as at the completion of configuration. All internal storage elements are reset. If not used, PWRDWN must be tied to Vcc. |

| RESET         | This is an active-low input which has three functions:                                                                                                                                                                                                                                                                                                                                                                    |

|               | <ul> <li>Prior to the start of configuration, a low input will delay the start of the configuration process.<br/>An internal circuit senses the application of power and begins a minimal time-out cycle. When<br/>the time-out and RESET are complete, the levels of the M lines are sampled and configuration<br/>begins.</li> </ul>                                                                                    |

|               | <ul> <li>If RESET is asserted during a configuration, the FPGA is reinitialized and will restart the con-<br/>figuration at the termination of RESET.</li> </ul>                                                                                                                                                                                                                                                          |

|               | <ul> <li>If RESET is asserted after configuration is complete, it will provide an asynchronous reset of all<br/>IOB and CLB storage elements of the FPGA.</li> </ul>                                                                                                                                                                                                                                                      |

| CCLK          | <b>Configuration Clock</b> . During configuration, this is an output of an FPGA in master mode or peripheral mode. FPGAs in slave mode use it as a clock input. During a readback operation, it is a clock input for the configuration data being filtered out.                                                                                                                                                           |

| DONE/<br>PROG | <b>DONE Output</b> . Configurable as open drain with or without an internal pull-up resistor. At the completion of configuration, the circuitry of the FPGA becomes active in a synchronous order, and DONE may be programmed to occur one cycle before or after that occurs. Once configuration is done, a high-to-low transition of this pin will cause an initialization of the FPGA and start a reconfiguration.      |

| M0/RTRIG      | <b>Mode 0</b> . This input, M1, and M2 are sampled before the start of configuration to establish the configuration mode to be used. After configuration is complete, a low-to-high transition acts as a read trigger to initiate a readback of configuration and storage-element data clocked by CCLK.                                                                                                                   |

| M1/RDATA      | <b>Mode 1</b> . This input, M0, and M2 are sampled before the start of configuration to establish the configuration mode to be used. After configuration is complete, this pin is the active-low output of the readback data.                                                                                                                                                                                             |

# Pin Information (continued)

| Symbol               | Name/Description                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M2                   | <b>Mode 2</b> . This input has a passive pull-up during configuration. Together with M0 and M1, it is sampled before the start of configuration to establish the configuration mode to be used. After configuration, this pin becomes a user-programmable I/O pin.                                                                                                                                                                                    |

| HDC                  | <b>High During Configuration</b> . HDC is held at a high level by the FPGA until after configuration. It is available as a control output indicating that configuration is not yet completed. After configuration, this pin is a user I/O pin.                                                                                                                                                                                                        |

| LDC                  | <b>Low During Configuration</b> . This active-low signal is held at a low level by the FPGA until after configuration. It is available as a control output indicating that configuration is not yet completed. It is particularly useful in master mode as a low enable for an EPROM. After configuration, this pin is a user I/O pin. If used as a low EPROM enable, it must be programmed as a high after configuration.                            |

| ĪNIT                 | This is an active-low, open-drain output which is held low during the power stabilization and internal clearing of the configuration memory. It can be used to indicate status to a configuring microprocessor or, as a wired-AND of several slave mode devices, a hold-off signal for a master mode device. After configuration, this pin becomes a user-programmable I/O pin.                                                                       |

| BCLKIN               | This is a direct CMOS level input to the alternate clock buffer (auxiliary buffer) in the lower right corner.                                                                                                                                                                                                                                                                                                                                         |

| XTL1                 | This user I/O pin can be used to operate as the output of an amplifier driving an external crystal and bias circuitry.                                                                                                                                                                                                                                                                                                                                |

| XTL2                 | This user I/O pin can be used as the input of an amplifier connected to an external crystal and bias circuitry. The I/O block is left unconfigured. The oscillator configuration is activated by routing a net from the oscillator buffer symbol output and by the <i>ORCA</i> Foundry bit stream generation program.                                                                                                                                 |

| CS0, CS1,<br>CS2, WS | These four inputs represent a set of signals, three active-low and one active-high, which are used in the peripheral mode to control configuration data entry. The assertion of all four generates a write to the internal data buffer. The removal of any assertion clocks in the D[7:0] data present. In the master parallel mode, $\overline{WS}$ and CS2 are the A0 and A1 outputs. After configuration, the pins are user-programmable I/O pins. |

# Pin Information (continued)

#### Table 5. I/O Pins with Special Functions (continued)

| Symbol   | Name/Description                                                                                                                                                                                                                                                       |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RCLK     | During master parallel mode configuration, RCLK represents a read of an external dynamic memory device (normally not used).                                                                                                                                            |

| RDY/BUSY | During peripheral parallel mode configuration, this pin indicates when the chip is ready for another byte of data to be written to it. After configuration is complete, this pin becomes a user-programmed I/O pin.                                                    |

| D[7:0]   | This set of eight pins represents the parallel configuration byte for the parallel master and peripheral modes. After configuration is complete, they are user-programmed I/O pins.                                                                                    |

| A[15:0]  | This set of 16 pins presents an address output for a configuration EPROM during master parallel mode. After configuration is complete, they are user-programmed I/O pins.                                                                                              |

| DIN      | This user I/O pin is used as serial data input during slave or master serial configuration. This pin is data zero input in master or peripheral configuration mode.                                                                                                    |

| DOUT     | This user I/O pin is used during configuration to output serial configuration data for daisy-<br>chained slaves' data in.                                                                                                                                              |

| TCLKIN   | This is a direct CMOS level input to the global clock buffer.                                                                                                                                                                                                          |

| I/O      | <b>Input/Output (Unrestricted)</b> . May be programmed by the user to be input and/or output pin following configuration. Some of these pins present a high-impedance pull-up (see next page) or perform other functions before configuration is complete (see above). |

### Pin Information (continued)

#### Table 6A. ATT3000 Family Configuration (44, 68, and 84 PLCC; 100 QFP; and 100 TQFP)

| Configuration Mode (M2:M1:M0) |                          |                       |                        | 60                    | 04          | 100        | 100                     | lloor      |             |                   |

|-------------------------------|--------------------------|-----------------------|------------------------|-----------------------|-------------|------------|-------------------------|------------|-------------|-------------------|

| Slave<br>(1:1:1)              | Master-Serial<br>(0:0:0) | Peripheral<br>(1:0:1) | Master-High<br>(1:1:0) | Master-Low<br>(1:0:0) | 44<br>PLCC* | 68<br>PLCC | 84<br>PLCC <sup>†</sup> | 100<br>QFP | 100<br>TQFP | User<br>Operation |

| PWRDWN                        | PWRDWN                   | PWRDWN                | PWRDWN                 | PWRDWN                | 7           | 10         | 12                      | 29         | 26          | PWRDWN            |

| Vcc                           | Vcc                      | Vcc                   | Vcc                    | Vcc                   | 12          | 18         | 22                      | 41         | 38          | Vcc               |

| M1 (High)                     | M1 (Low)                 | M1 (Low)              | M1 (High)              | M1 (Low)              | 16          | 25         | 31                      | 52         | 49          | RDATA             |

| M0 (High)                     | M0 (Low)                 | M0 (Low)              | M0 (High)              | M0 (Low)              | 17          | 26         | 32                      | 54         | 51          | RTRIG             |

| M2 (High)                     | M2 (Low)                 | M2 (High)             | M2 (High)              | M2 (Low)              | 18          | 27         | 33                      | 56         | 53          | I/O               |