#### Features

- 5V tolerant Inputs and Outputs

- 24 mA balanced drive outputs

- Low power, pin-compatible replacement for LCX, LPT, LVC, LVCH & LVT families

- FCT-C speed at 5.4 ns

- · Power-off disable outputs permits live insertion

- Edge-rate control circuitry for significantly improved noise characteristics

- Typical output skew < 250 ps

- ESD > 2000V

- TSSOP (19.6-mil pitch) and SSOP (25-mil pitch) packages

- Extended commercial temperature range of -40°C to +85°C

- V<sub>CC</sub> = 2.7V to 3.6V

- Typical V<sub>OLP</sub> (ground bounce) <0.6V at V<sub>CC</sub> = 3.3V, T<sub>A</sub>= 25°C

# CY74FCT163646

# 16-Bit Registered Transceiver

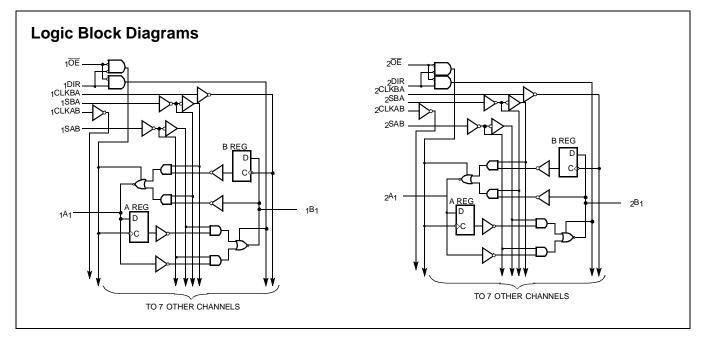

### **Functional Description**

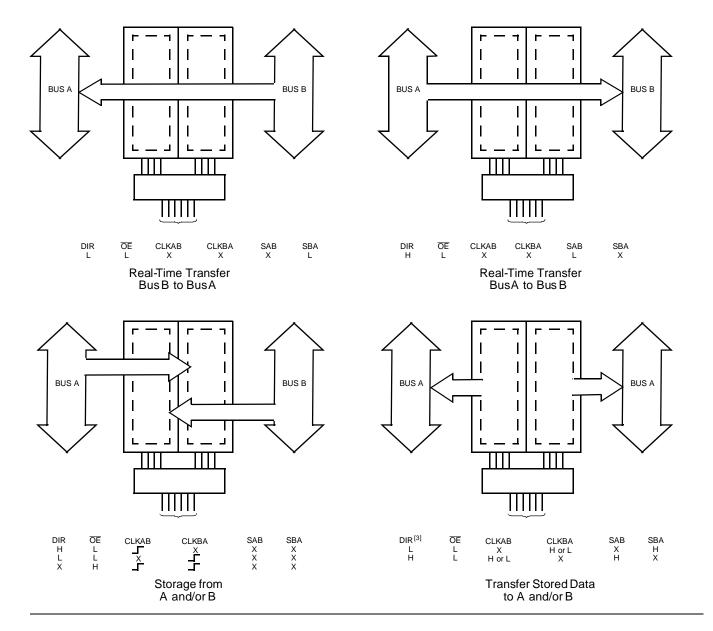

The CY74FCT163646 16-bit transceiver is a three-state, D-type register, and control circuitry arranged for multiplexed transmission of data directly from the input bus or from the internal registers. Data on the A or B bus will be clocked into the registers as the appropriate clock pin goes to a HIGH logic level. Output Enable ( $\overline{OE}$ ) and direction pins (DIR) are provided to control the transceiver function. In the transceiver mode, data present at the high impedance port may be stored in either the A or B register, or in both. The select controls can multiplex stored and real-time (transparent mode) data. The direction control determines which bus will receive data when the Output Enable ( $\overline{OE}$ ) is Active LOW. In the isolation mode (Output Enable ( $\overline{OE}$ ) HIGH), A data may be stored in the B register and/or B data may be stored in the A register.

The CY74FCT163646 has 24-mA balanced output drivers with current limiting resistors in the outputs. This reduces the need for external terminating resistors and provides for minimal undershoot and reduced ground bounce. The inputs and outputs were designed to be capable of being driven by 5.0 V busses, allowing them to be used in mixed voltage systems as translators. The outputs are also designed with a power-off disable feature enabling them to be used in applications requiring live insertion.

# **Pin Configuration**

|                  | - | SOP/TS<br>Top Vie |    | )P |                   |

|------------------|---|-------------------|----|----|-------------------|

| 1DIR             | Г |                   | 56 | Ь  | 10E               |

| 1CLKAB           |   | 2                 | 55 |    | 1CLKBA            |

| 1SAB             |   | 3                 | 54 |    | 1SBA              |

| GND              |   | 4                 | 53 |    | GND               |

| 1A1              |   | 5                 | 52 |    | 1 <sup>B</sup> 1  |

| 1 <sup>A</sup> 2 | Г | 6                 | 51 | Þ  | 1 <sup>B</sup> 2  |

| VCC              |   | 7                 | 50 |    | VCC               |

| 1A3              |   | 8                 | 49 |    | 1B3               |

| 1A4              |   | 9                 | 48 | 口  | 1B4               |

| 1 <sup>A</sup> 5 |   | 10                | 47 |    | 1 <sup>B</sup> 5  |

| GND              | Г | 11                | 46 |    | GND               |

| 1 <sup>A</sup> 6 |   | 12                | 45 |    | 1 <sup>B</sup> 6  |

| 1 <sup>A</sup> 7 | Г | 13                | 44 | Þ  | 1B7               |

| 1 <sup>A</sup> 8 |   | 14                | 43 |    | 1 <sup>B</sup> 8  |

| 2A1              | Г | 15                | 42 |    | 2 <sup>B</sup> 1  |

| 2A2              |   | 16                | 41 |    | 2B2               |

| 2A3              | Г | 17                | 40 |    | 2B3               |

| GND              |   | 18                | 39 |    | GND               |

| 2A4              |   | 19                | 38 | Þ  | 2B4               |

| 2A5              |   | 20                | 37 |    | 2 <sup>B</sup> 5  |

| 2 <sup>A</sup> 6 |   | 21                | 36 | Þ  | 2 <sup>B</sup> 6  |

| VCC              |   | 22                | 35 |    | VCC               |

| 2A7              | Г | 23                | 34 |    | 2B7               |

| 2 <sup>A</sup> 8 | Г | 24                | 33 |    | 2 <sup>B</sup> 8  |

| GND              |   | 25                | 32 |    | GND               |

| 2SAB             | Г | 26                | 31 |    | 2SBA              |

| 2CLKAB           |   | 27                | 30 | Þ  | 2CLKBA            |

| 2DIR             | Ц | 28                | 29 | P  | 2 <mark>0E</mark> |

### **Pin Description**

| Pin Names    | Description                                    |  |  |  |

|--------------|------------------------------------------------|--|--|--|

| A            | Data Register A Inputs Data Register B Outputs |  |  |  |

| В            | Data Register B Inputs Data Register A Outputs |  |  |  |

| CLKAB, CLKBA | Clock Pulse Inputs                             |  |  |  |

| SAB, SBA     | Output Data Source Select Inputs               |  |  |  |

| DIR          | Direction                                      |  |  |  |

| ŌĒ           | Output Enable (Active LOW)                     |  |  |  |

### Function Table<sup>[1]</sup>

| Inputs |     |        |        |     |     | Data   | <b>I/O</b> <sup>[2]</sup> | Function                  |  |

|--------|-----|--------|--------|-----|-----|--------|---------------------------|---------------------------|--|

| ŌE     | DIR | CLKAB  | CLKBA  | SAB | SBA | Α      | В                         | Function                  |  |

| Н      | Х   | H or L | H or L | Х   | Х   | Input  | Input                     | Isolation                 |  |

| Н      | Х   |        |        | Х   | Х   |        |                           | Store A and B Data        |  |

| L      | L   | Х      | Х      | Х   | L   | Output | Input                     | Real Time B Data to A Bus |  |

| L      | L   | Х      | H or L | Х   | Н   |        |                           | Stored B Data to A Bus    |  |

| L      | Н   | Х      | Х      | L   | Х   | Input  | Output                    | Real Time A Data to Bus   |  |

| L      | Н   | H or L | Х      | Н   | Х   |        |                           | Stored A Data to B Bus    |  |

Notes:

H = HIGH Voltage Level, L = LOW Voltage Level, X = Don't Care,  $\square$  = LOW-to-HIGH Transition The data output functions may be enabled or disabled by various signals at the OE or DIR inputs. Data input functions are always enabled, i.e., data at the bus pins will be stored on every LOW-to-HIGH transition on the clock inputs. 1. 2.

# CY74FCT163646

#### Maximum Ratings<sup>[4]</sup>

(Above which the useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature                       | –55°C to +125°C |

|-------------------------------------------|-----------------|

| Ambient Temperature with<br>Power Applied | –55°C to +125°C |

| Supply Voltage Range                      | 0.5V to +4.6V   |

| DC Input Voltage                          | –0.5V to +7.0V  |

| DC Output Voltage                                          | –0.5V to +7.0V |

|------------------------------------------------------------|----------------|

| DC Output Current<br>(Maximum Sink Current/Pin)            | –60 to +120 mA |

| Power Dissipation                                          | 1.0W           |

| Static Discharge Voltage<br>(per MIL-STD-883, Method 3015) | >2001V         |

| Range      | Ambient<br>Temperature | v <sub>cc</sub> |

|------------|------------------------|-----------------|

| Commercial | – 40°C to +85°C        | 2.7V to 3.6V    |

#### Notes:

3. 4.

Cannot transfer data to A-bus and B-bus simultaneously. Stresses greater than those listed under Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

| Parameter        | Description                                                | Test Conditions                                                      | Min.                 | <b>Typ.</b> <sup>[5]</sup> | Max. | Unit |

|------------------|------------------------------------------------------------|----------------------------------------------------------------------|----------------------|----------------------------|------|------|

| V <sub>IH</sub>  | Input HIGH Voltage                                         | All Inputs                                                           | 2.0                  |                            | 5.5  | V    |

| V <sub>IL</sub>  | Input LOW Voltage                                          |                                                                      |                      |                            | 0.8  | V    |

| V <sub>H</sub>   | Input Hysteresis <sup>[6]</sup>                            |                                                                      |                      | 100                        |      | mV   |

| V <sub>IK</sub>  | Input Clamp Diode Voltage                                  | V <sub>CC</sub> =Min., I <sub>IN</sub> =-18 mA                       |                      | -0.7                       | -1.2 | V    |

| I <sub>IH</sub>  | Input HIGH Current                                         | V <sub>CC</sub> =Max., V <sub>I</sub> =5.5V                          |                      |                            | ±1   | μΑ   |

| IIL              | Input LOW Current                                          | V <sub>CC</sub> =Max., V <sub>I</sub> =GND                           |                      |                            | ±1   | μΑ   |

| I <sub>OZH</sub> | High Impedance Output Current<br>(Three-State Output pins) | V <sub>CC</sub> =Max., V <sub>OUT</sub> =5.5V                        |                      |                            | ±1   | μA   |

| I <sub>OZL</sub> | High Impedance Output Current<br>(Three-State Output pins) | V <sub>CC</sub> =Max., V <sub>OUT</sub> =GND                         |                      |                            | ±1   | μA   |

| I <sub>ODL</sub> | Output LOW Current <sup>[7]</sup>                          | $V_{CC}$ =3.3V, $V_{IN}$ = $V_{IH}$<br>or $V_{IL}$ , $V_{OUT}$ =1.5V |                      |                            | 200  | mA   |

| I <sub>ODH</sub> | Output HIGH Current <sup>[7]</sup>                         | $V_{CC}$ =3.3V, $V_{IN}$ = $V_{IH}$<br>or $V_{IL}$ , $V_{OUT}$ =1.5V |                      |                            | -110 | mA   |

| V <sub>OH</sub>  | Output HIGH Voltage                                        | V <sub>CC</sub> =Min., I <sub>OH</sub> = -0.1 mA                     | V <sub>CC</sub> -0.2 |                            |      | V    |

|                  |                                                            | V <sub>CC</sub> =3.0V, I <sub>OH</sub> = -8 mA                       | 2.4 <sup>[8]</sup>   | 3.0                        |      |      |

|                  |                                                            | V <sub>CC</sub> =3.0V, I <sub>OH</sub> = -24 mA                      | 2.0                  | 3.0                        |      |      |

| V <sub>OL</sub>  | Output LOW Voltage                                         | V <sub>CC</sub> =Min., I <sub>OL</sub> = 0.1mA                       |                      |                            | 0.2  | V    |

|                  |                                                            | V <sub>CC</sub> =Min., I <sub>OL</sub> = 24 mA                       |                      | 0.3                        | 0.5  |      |

| I <sub>OS</sub>  | Short Circuit Current <sup>[7]</sup>                       | V <sub>CC</sub> =Max., V <sub>OUT</sub> =GND -60 -135                |                      | -135                       | -240 | mA   |

| I <sub>OFF</sub> | Power-Off Disable                                          | V <sub>CC</sub> =0V, V <sub>OUT</sub> ≤4.5V                          |                      |                            | ±100 | μA   |

# Electrical Characteristics Over the Operating Range V<sub>CC</sub>=2.7V to 3.6V

## **Capacitance**<sup>[5]</sup> (T<sub>A</sub> = +25°C, f = 1.0 MHz)

| Symbol           | Description <sup>[9]</sup> | Conditions           | Тур. | Max. | Unit |

|------------------|----------------------------|----------------------|------|------|------|

| C <sub>IN</sub>  | Input Capacitance          | V <sub>IN</sub> = 0V | 4.5  | 6.0  | pF   |

| C <sub>OUT</sub> | Output Capacitance         | V <sub>OUT</sub> =0V | 5.5  | 8.0  | pF   |

Notes:

Typical values are at V<sub>CC</sub>=3.3V, T<sub>A</sub>=+25°C ambient.

This parameter is guaranteed but not tested.

Not more than one output should be shorted at a time. Duration of short should not exceed one second. The use of high-speed test apparatus and/or sample and hold techniques are preferable in order to minimize internal chip heating and more accurately reflect operational values. Otherwise prolonged shorting of a high output may raise the chip temperature well above normal and thereby cause invalid readings in other parametrics tests. In any sequence of parameter tests, I<sub>OS</sub> tests should be performed last.

V<sub>OH</sub>=V<sub>CC</sub>-0.6 V at rated current.

This parameter is measured at characterization but not tested.

# **Power Supply Characteristics**

| Parame-<br>ter   | Description                                       | Test Conditions                                                                                    |                                                                   | <b>Typ.</b> <sup>[5]</sup> | Max.                | Unit   |

|------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------------|---------------------|--------|

| I <sub>CC</sub>  | Quiescent Power Supply Current                    | V <sub>CC</sub> =Max.                                                                              | V <sub>IN</sub> ≤0.2V<br>V <sub>IN</sub> ≥V <sub>CC</sub> −0.2V   | 0.1                        | 10                  | μΑ     |

| $\Delta I_{CC}$  | Quiescent Power Supply Current<br>TTL Inputs HIGH | V <sub>CC</sub> =Max.                                                                              | V <sub>IN</sub> =V <sub>CC</sub> -0.6V <sup>[10]</sup>            | 2.0                        | 30                  | μΑ     |

| I <sub>CCD</sub> | Dynamic Power Supply<br>Current <sup>[11]</sup>   | V <sub>CC</sub> =Max., Outputs Open<br>DIR=OE=GND<br>One-Bit Toggling<br>50% Duty Cycle            | V <sub>IN</sub> =V <sub>CC</sub> or<br>V <sub>IN</sub> =GND       | 50                         | 75                  | μA/MHz |

| I <sub>C</sub>   | Total Power Supply Current <sup>[12]</sup>        | V <sub>CC</sub> =Max.,Outputs Open<br>f <sub>o</sub> =10 MHz (CLKBA)                               | V <sub>IN</sub> =V <sub>CC</sub> or<br>V <sub>IN</sub> =GND       | 0.5                        | 0.8                 | mA     |

|                  |                                                   | 50% Duty Cycle<br>DIR=OE=GND<br>One-Bit Toggling, f <sub>1</sub> =5 MHz,<br>50% Duty Cycle         | V <sub>IN</sub> =V <sub>CC</sub> -0.6V or<br>V <sub>IN</sub> =GND | 0.5                        | 0.8                 |        |

|                  |                                                   | V <sub>CC</sub> =Max., Outputs Open<br>f <sub>o</sub> =10 MHz (CLKBA)                              | V <sub>IN</sub> =V <sub>CC</sub> or<br>V <sub>IN</sub> =GND       | 2.5                        | 3.8 <sup>[13]</sup> |        |

|                  |                                                   | 50% Duty Cycle<br>DIR=OE=GND<br>Sixteen-Bits Toggling<br>f <sub>1</sub> =2.5 MHz<br>50% Duty Cycle | V <sub>IN</sub> =V <sub>CC</sub> -0.6V or<br>V <sub>IN</sub> =GND | 2.6                        | 4.1 <sup>[13]</sup> |        |

Notes:

- Notes:10. Per TTL driven input); all other inputs at  $V_{CC}$  or GND.11. This parameter is not directly testable, but is derived for use in Total Power Supply calculations.12.  $I_C = I_{QUESCENT} + I_{NPUTS} + I_{DYNAMIC}$  $I_C = I_{CC} + \Delta I_{CC} D_H N_T + I_{CCD} (f_0 N_C / 2 + f_1 N_1)$  $I_C = Quiescent Current with CMOS input levels$  $\Delta I_{CC}$  = Power Supply Current for a TTL HIGH input $D_H$  = Duty Cycle for TTL inputs HIGH $N_T$  = Number of TTL inputs at  $D_H$  $I_{CCD}$  = Dynamic Current caused by an input transition pair (HLH or LHL) $f_0$  = Clock frequency for registered devices, otherwise zero $N_C$  = Number of clock inputs changing at  $f_1$  $f_1$  = Input signal frequency $N_1$  = Number of inputs changing at  $f_1$ All currents are in milliamps and all frequencies are in megahertz.13. Values for these conditions are examples of the I<sub>CC</sub> formula. These limits are guaranteed but not tested.

|                                      |                                         | CY74FCT | 163646A | CY74FCT | 163646C |      |                          |

|--------------------------------------|-----------------------------------------|---------|---------|---------|---------|------|--------------------------|

| Parameter                            | Description                             | Min.    | Max.    | Min.    | Max.    | Unit | Fig. No. <sup>[16]</sup> |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>Bus to Bus         | 1.5     | 6.3     | 1.5     | 5.4     | ns   | 1, 2                     |

| t <sub>PZH</sub><br>t <sub>PZL</sub> | Output Enable Time<br>DIR or OE to Bus  | 1.5     | 9.8     | 1.5     | 7.8     | ns   | 1, 7, 8                  |

| t <sub>PHZ</sub><br>t <sub>PLZ</sub> | Output Disable Time<br>DIR or OE to Bus | 1.5     | 6.3     | 1.5     | 6.3     | ns   | 1, 7, 8                  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>Clock to Bus       | 1.5     | 6.3     | 1.5     | 5.7     | ns   | 1, 5                     |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>SBA or SAB to Bus  | 1.5     | 7.7     | 1.5     | 6.2     | ns   | 1,5                      |

| t <sub>SU</sub>                      | Set-Up Time HIGH or<br>LOW Bus to Clock | 2.0     | —       | 2.0     | —       | ns   | 4                        |

| t <sub>H</sub>                       | Hold Time HIGH or<br>LOW Bus to Clock   | 1.5     | —       | 1.5     | —       | ns   | 4                        |

| t <sub>W</sub>                       | Clock Pulse Width<br>HIGH or LOW        | 5.0     | —       | 5.0     | —       | ns   | 6                        |

| t <sub>SK(O)</sub>                   | Output Skew <sup>[17]</sup>             | —       | 0.5     | —       | 0.5     | ns   | _                        |

# Switching Characteristics Over the Operating Range $V_{CC}$ =3.0V to 3.6V<sup>[14,15]</sup>

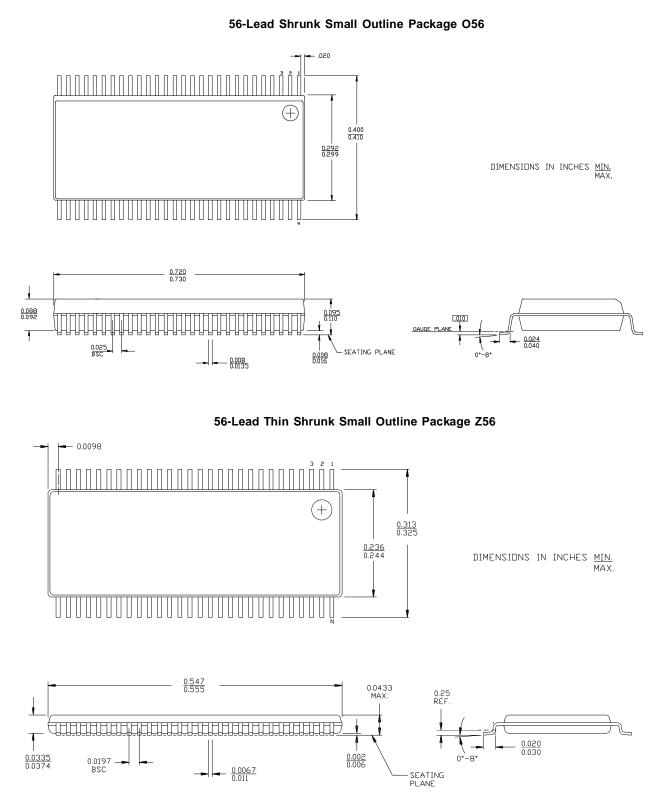

#### Ordering Information CY74FCT163646

| Speed<br>(ns) | Ordering Code     | Package<br>Name | Package Type            | Operating<br>Range |

|---------------|-------------------|-----------------|-------------------------|--------------------|

| 5.4           | CY74FCT163646CPAC | Z56             | 56-Lead (240-Mil) TSSOP | Commercial         |

|               | CY74FCT163646CPVC | O56             | 56-Lead (300-Mil) SSOP  |                    |

| 6.3           | CY74FCT163646APAC | Z56             | 56-Lead (240-Mil) TSSOP | Commercial         |

|               | CY74FCT163646APVC | O56             | 56-Lead (300-Mil) SSOP  |                    |

Notes:

Minimum limits are guaranteed but not tested on Propagation Delays.

For V<sub>CC</sub> =2.7, propagation delay, output enable and output disable times should be degraded by 20%.

See "Parameter Measurement Information" in the General Information section.

Skew any two outputs of the same package switching in the same direction. This parameter is guaranteed by design.

Document #: 38-00575

### **Package Diagrams**

© Cypress Semiconductor Corporation, 1997. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of charges.